在计算机硬件生态环境中,DDR4内存占据着主力军位置。身为一位电脑热爱者,我深谙内存对主机性能的重大影响。新品DDR4内存到手后,我立即着手进行时序设定深入研究。虽然未曾料到在此过程中会遇如此多难题,但今日仍愿与各位一同共享实战经验。

第一坑:了解自己的内存

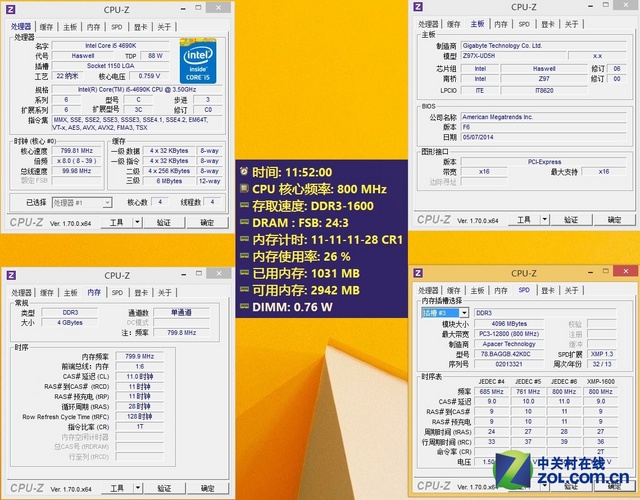

初始时序校正前,须先掌握所购DDR4内存确切参数——主频与时序,方法为查看内存模块标签或查询制造商官网的相应数据。唯有了然于心,方可精准地调节时序。

第二坑:选择合适的主板和BIOS版本

由于各类主板及BIOS版本对时序调整操作的支持存在差异,为尽量避免潜在冲突,我对所用主板及BIOS版本进行详细了解后再开始执行此项任务,同时保证其充分支持我购入之内存模块以确保稳定运行。

第三坑:备份重要数据

在事件序列调整中,潜在问题可能引发系统崩溃甚至数据遗失。为防事故发生,我已提前做好重要数据备份,以避免此类遗憾发生。

第四坑:小心调整参数

在时序调整过程中,我们必须借助于BIOS界面来有效更改内存在关的参数配置。然而,这势必会对系统稳定性产生潜在影响。因此,为规避可能出现的风险,我们采取慎重且逐步式的调整策略,同时在每次参数修正后执行测试与稳定性评价。

第五坑:注意电压设置

DDR4内存时序的精确设定亦需考虑电压值的调控。不当的电压设置有引发内存故障乃至影响系统稳定性之虞。为了确保电压适宜,首先研究了内存制造商所提供的建议电压区间,再根据实际情形细微调整得以实现。

第六坑:反复测试与优化

时序调整为持续优化过程,历经多次调试与验证。每当参数改进完成之后,我都会运用诸如 Prime95 和 MemTest86+等压力测试工具,确保提高系统稳定性及内存性能。

第七坑:记录每次调整

每逢调校后,我均会详实记载各相关参数的变化状况,以确保理解并掌握系统运作情况,同时为未来调校提供参考价值,避免不必要的重复工作。

第八坑:与他人交流与学习

在时序调试这个复杂且技术难度较高的领域中,我通过参与计算机硬件研讨会及相关论坛,积极与其他同行进行深入交流与学习,以提升自我能力,进一步攻克难题。

第九坑:享受调整的乐趣

虽然时序调整旅程充满波折与挑战,然而关键在于享受其间的无穷乐趣。经过不懈努力与求索,我技术得以精进,更深刻地领悟这一神秘且引人入胜的领域。

奢侈品的调价并非易事,一旦拥有充足的耐性与热情,定可使每一位消费者发挥出DDR4内存的最高性能。此经历旨在为同样致力于优化时序之士提供启示及助力。共勉之,共同开创属于你我的DDR4内存调整之路!