本文旨在从一名资深电脑硬件工程师的独特角度出发,针对DDR3约束这一主题进行深入理解与探讨。借助丰富详实的案例讲解及深度剖析,我们力求为读者呈现出关于DDR3约束的多元化解读,使其能更娴熟地应对相关技术挑战。

1.什么是ddr3约束?

DR3制约即为确保内存体系正常运作而需遵循的时序规范。其内容涵盖了诸多因素如时钟速度、时序关联性以及延迟等。

2. ddr3约束的种类有哪些?

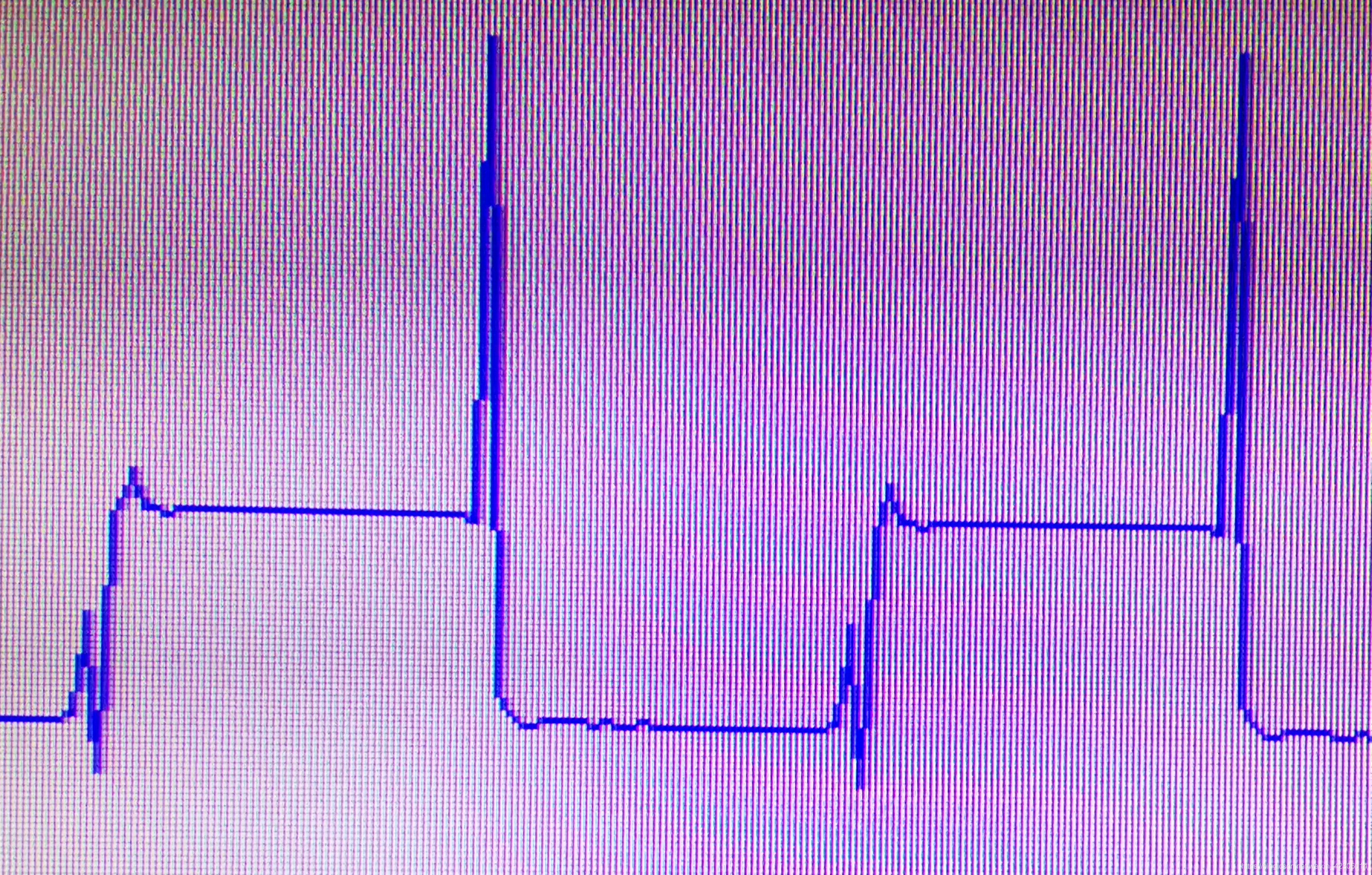

-"时钟频率约束"规定:要保证存储器控制组件与内存储存模件间的运行标准相同,不然会引发数据传输失误。

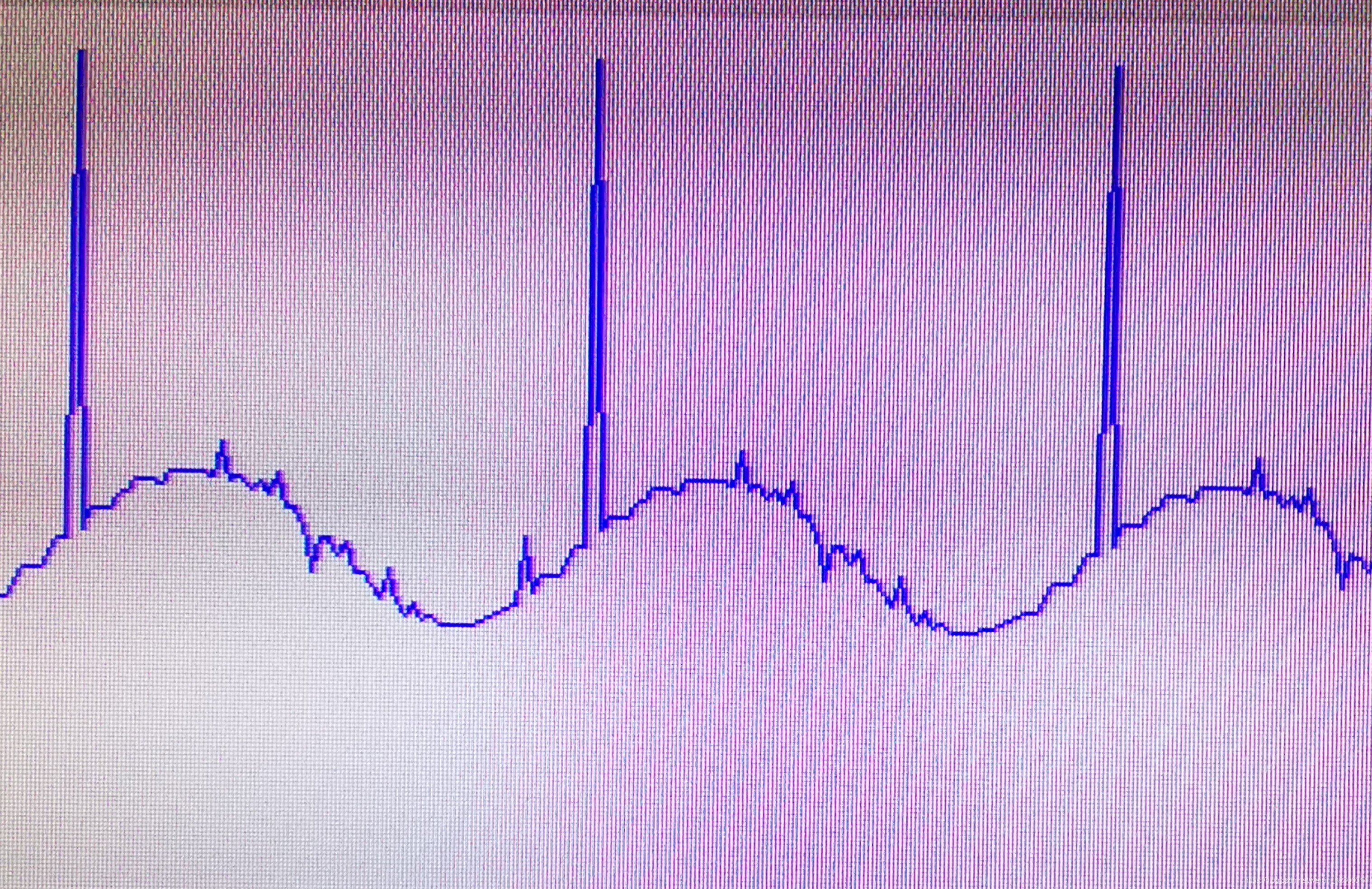

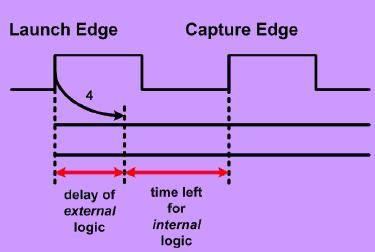

首先,我们需要遵循先后次序的制约,即确保数据能在特定时间段内准确抵达目标地,以免出现数据传输滞后或误报的情况。

-延迟约束:信号须在规定时间段内抵达终点,否则会引发数据传输的故障。

3.如何应对ddr3约束?

-优选内存控制单元及内存模组:鉴于系统规格与DDR3规范限定,择优挑选兼容性佳的硬件部件,以确保其有效协同工作。

-优化布局结构:科学拟定信号路径,减轻延迟及干扰程度,提升数据传递速率。

-时序参数调控:依据特定需求,对内存控制器的时序参数进行合理调节,确保遵守DDR3的限制标准。

运用仿真平台,严谨验证:采用仿真手段模拟现实运行环境,确保系统在DDR3的严格要求下正常工作。

4. ddr3约束带来的挑战有哪些?

-复杂性:DDR3遵循多维度的约束原则,需系统评估各项要素,合理进行调整处理。

-对容错性的严格要求:倘若DRAM3的约束条件受到损害,将引发严重的问题如系统失效及数据遗失等。

-时序优化的挑战性颇高:需深度理解硬件设计,方能调整恰当的时序参数,历经多次试验与验证。

5.如何解决ddr3约束带来的挑战?

-深化硬件设计知识深度:理解DDR3约束原由及相关知识,熟练调整时序参数技能。

持续磨砺与提升:通过实战项目的规划与调试,丰富经验,不断完善创意。

-交流共享:参与行业学术研讨会及论坛,以获取最新的技术信息并与业内专家共同探讨问题并提供解决策略。

6. ddr3约束对系统性能的影响如何?

-效能改善:遵循DDR3具体规范可增强存储器系统稳定性与可靠性,进而提升整体系统运行性能。

-提升数据传输速率:通过改进电路布局与优化时序参数相结合的手段,能够显著加快数据传输的速率,相应地缩短延迟时间。

7.如何评估ddr3约束的合理性?

-运用仿真工具验证:借由专业仿真软件针对ddr3边界条件的模拟及验算,确保设备能遵循约束标准

-落实实战检验:于实体硬件环境下实施测试,查找及修复可能出现的DDR3受限问题。

针对上文所述的七个要点进行精细阐述,相信各位读者在理解并掌握DDR3限制问题方面已然有了更深层次的见解。针对此DDR3限定问题,采用合适的硬件构件,优化学术线路规划,调整精确时序报告,以及实施正确的模拟运行和现实效果检验,都是有效应对这段挑战,以提高系统效率和稳定性的重要手段。