1.设计思路的确立

身为资深的Verilog DDR设计师,我采取明确的设计理念,以数据传输与时序调控为重心,精心策划设计流程。同时,亦兼顾功耗与面积评估,力图实现设计的高效且可靠。

2.数据传输接口的设计

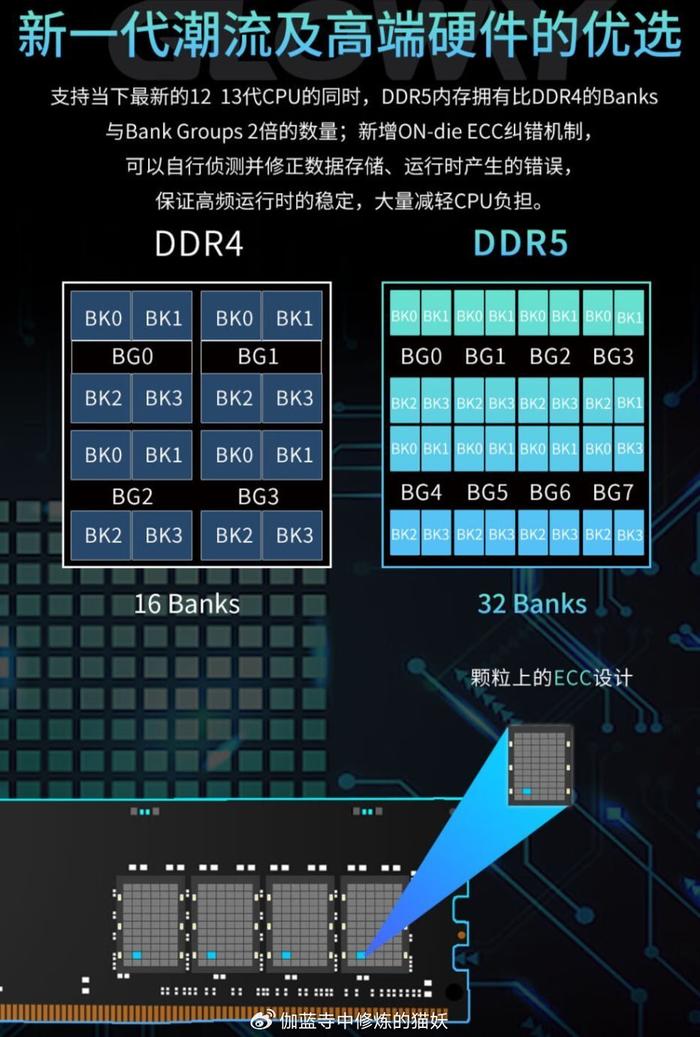

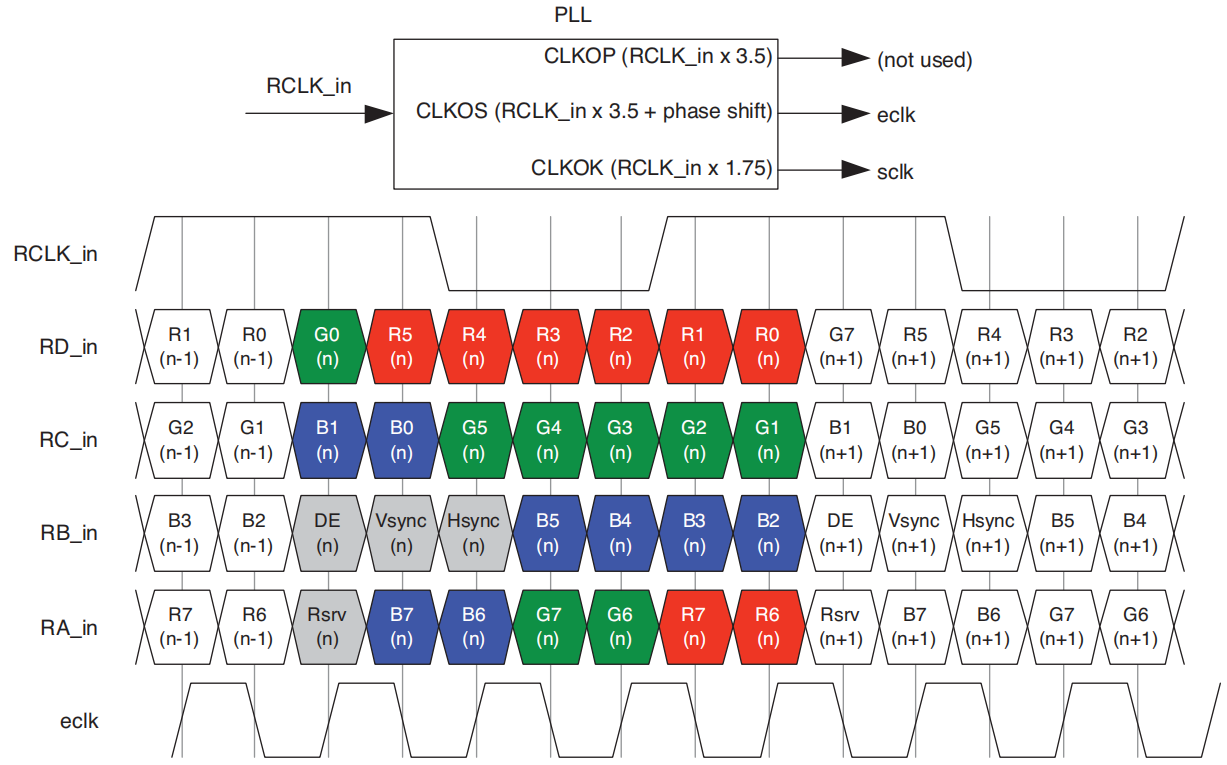

在设定数据传输接口时期,首选适当协议与接口规范,兼顾实际需求,考量采用DDR3、DDR4或LPDDR这类接口,以相应芯片与板级设计适应之。值得注意的是,务必关注数据传输速率、时钟频率等因素,以保证数据的稳定传送。

3.时序控制的优化

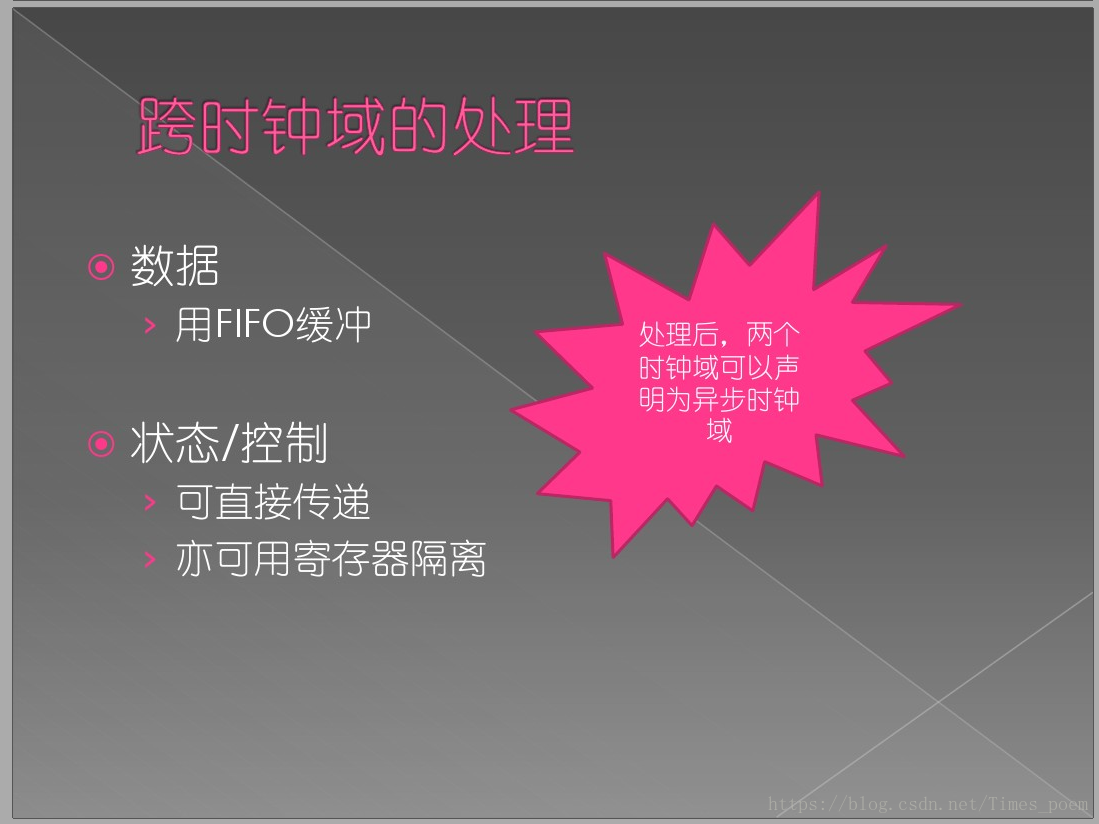

时序调控在DDR设计中拥显要地位。为提效增稳数据传送,我将精细调整时序设定。通过优化时钟延迟及信号采集所需时间等参数,降低信号抖动与时序偏离,从而提升DDR体系整体性能。

4.电源和地线的布局

在DDR技术设计过程中,必须重视电源与地线的布局安置问题。依照芯片设计需求以及板级整体布置计划,我将以科学严谨的思维对电源及地线上导线的走向和连接方式进行合理规划,从而降低信号干扰和功耗消耗,提升整个系统的稳定性与可靠性。

5.信号完整性分析

为确保数据传输的完整性,我们将开展信号完整性分析工作。专业工具如SI(Signal Integrity)可模拟并审查信号传输路径,揭示潜在的信号完整性缺陷,并据此实施优化策略。

6.时序调试方法

在DDR结构设计过程中,关键的步骤之一便是进行时序调整。我借助于如逻辑分析仪之类的仪器,实现时序的实时监控和调试。借助对时钟、数据及地址信号波形的细致考察,迅速地查出并修复问题,以保证时序操纵的精准无误。

7.异常情况处理经验

在实际DDR设计实践中,无所避免地会遭遇各种异常状况。凭借我多年的精密工程经验,我已积累了一套独特处理方法。例如,当时序失衡发生,可通过相应延长时钟周期或调整信号采集时机来解决;而碰到数据传输误差,则需仔细检查数据线路连通及信号干扰状况。

8.性能测试和验证

故此,在顺利完成DDR之设计后,将立即进行各项性能及可靠性测试与确认。其中包括运用各类测试工具与软件,全方位对DDR体系进行成熟而高效的功能及性能检测,以切实确保其稳定性及可靠性。此外,众多验证环节亦不可或缺,诸如时序验证、电压域验证等皆在此列。

9.不断学习和更新

身为DDR工程师,我深知行业的快速变更需要不断地学习与进步。为此,我尤为注重掌握新技术与新知识,关注整个产业的发展轨迹,以便于更新设计理念与策略。唯有如此,方能在DDR设计领域中维持竞争优势。

经过上述九个要点的实践与提炼,掌握了丰富VERILOG DDR设计经验。希望这些心得能助攻正从事或有意于此的同行匠人。让我们携手共进,为DDR技术的进步添砖加瓦!