身为一位经验丰富的硬件工程师,我熟知并深研DDR4内存时序之术。这是计算机系统中的重要技术,直接关系到内存的性能与稳定。下文我会深入剖析DDR4内存时序的方方面面,包括定义、重要性、参数解释以及提高性能的调参方法等等。

什么是DDR4内存时序?

DDR4内存时序,即是对那些规范和参数的一种统称。它们涉及到控制内存模组中数据传输流程以及处理次序的环节。在计算机体系结构内,为了满足准确读取和写入数据需求,各内存模组始终遵循着预先设定好的、严格定时的读写时序,这无疑体现出DDR4内存时序的重要性。实际上,DDR4内存时序就是对内存模组各类操作所须遵守的来去有据的时间规定。

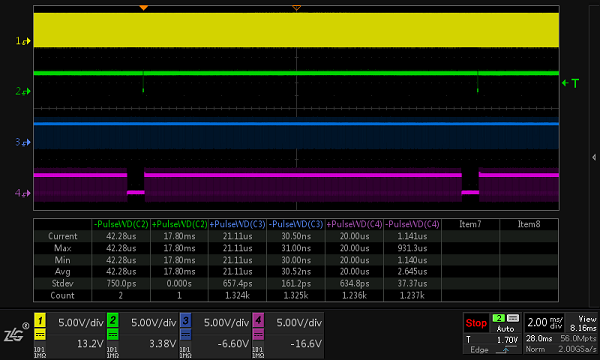

DDR4内存的时序参数主要包括CL(CAS Latency),tRCD,tRP以及tRAS四项,对内存模块与系统间响应时间及速率具有关键影响。精准调整此四项参数不仅可提高系统运行效率及稳定性,还能优化能耗管理。

为什么DDR4内存时序如此重要?

DDR4内存时序对系统性能及稳定至关紧要,因其直接影响到计算机读写速度以及反应效率。适度地调整DDR4内存时序能显著降低数据间潜伏期,提升传输速率与响应速度。反之,若时序设置不合适,可能引发数据读取错误、系统故障乃至设备损毁等严重后果。

面对如今高效能计算环境中大型数据库与人工智能、虚拟化等复杂应用挑战,对DDR4内存时序进行优化显得尤为关键。唯有深度理解并设定适当的DDR4内存时序参数,方能有效挖掘硬件设备的潜能,达到最佳性能水平。

DDR4内存时序参数的含义

知晓了DDR4内存时序的夯实基础之后,让我们深入浅出地说明几个常用的DDR4内存时序参数及它们所代表的意义。

- CL (CASLatency):描述了自列地址选通至开始数据输出的时间间隔。

- tRCD:行地址选通后多久才开始输出列地址上有效数据。

- tRP: PRECHARGE指令发布之后,会在特定时间内进行等待才能再度开启行址。

- tRAS:行地址选通后多久再次预充电或关闭。

调控这些关键参数直接关系到内存读取与写入效率及稳定运行。精细化调整相关数值大小,便于对系统性能进行精准调节和优化提升。

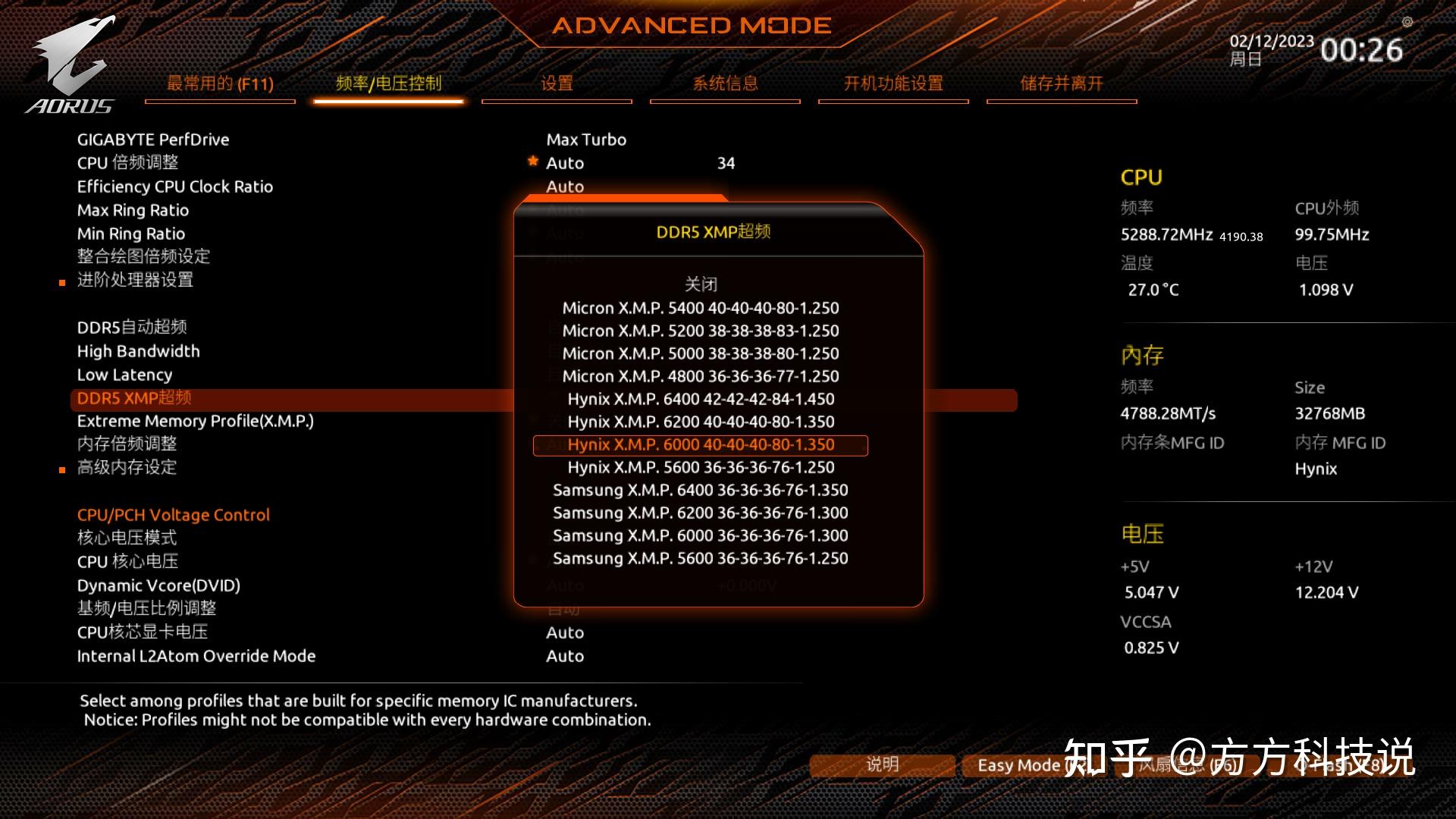

如何调整DDR4内存时序参数以提升性能?

在驾驶DDR4内存调整性能参数中,应依据实际情况进行严密分析与实验,并在保证其稳定运行之基础上逐一优化相应参数值。相关建议如下:

1.降低CL值:减小CAS延迟可提高读取效率。

调高tRCD数值:行地址至有效数据输出列地址期间,适当地延长过渡时段可进一步增强系统稳健性。

调整TPR和TRAS参数:通过合理控制PRECHARGE命令之后再度开启行地址以及在行地址选中之后再进行预充操作或者关闭的时长,能够有效地实现读写速率和稳定性之间的均衡。

在设置DDR4内存时钟参数时要慎重稳妥,同时应定期实施压力测试,确保系统稳定无误。

结语

本文对DDR4内存时序展开深度剖析,使我们更为透彻地感知其在计算机体系中的重大影响。恰当地调整DDR4内存时序参数,可提升系统效率及可靠性,并为各类应用环境下的运算作业提供更佳支撑。期望本文能激发大众读者的思考,使他们能够将所学的DDR4内存时序知识有效运用于实践操作之中。