DDR2电路设计乃是当下电子装置所广泛采纳之技艺,然而应用实践过程中往往面临诸多难题与困扰。以下拟就其中热点议题作出简要解答。

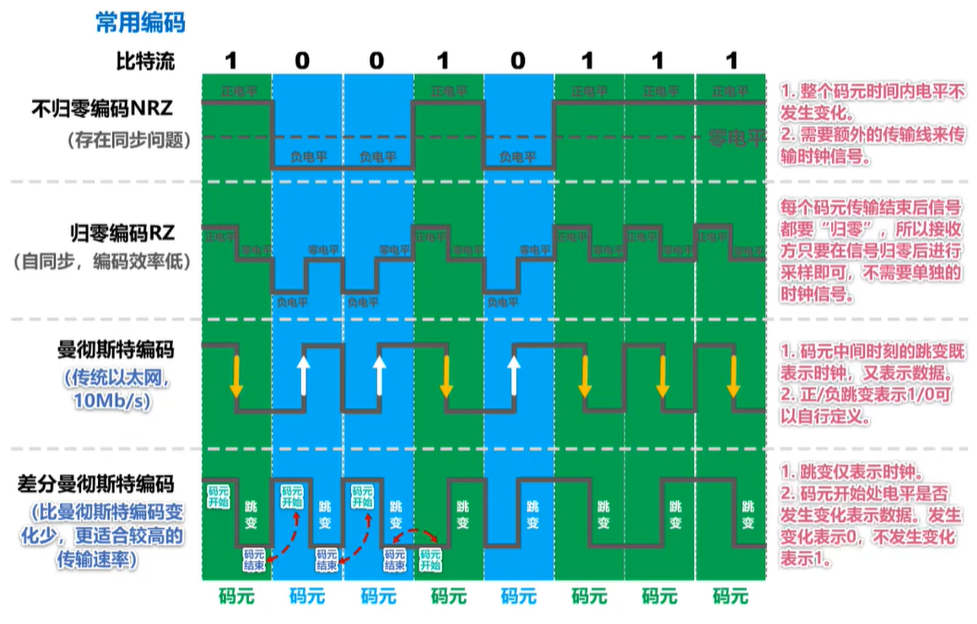

1. DDR2 布线有哪些基本原则?

面对DDR2设备布线工作,需关注其信号完整性、电磁兼容以及时钟分配问题。高效地完成这类工作,必须确保信号稳定且高速传送。

2.如何避免DDR2布线中的串扰问题?

为避免DDR2布线中的串扰问题,我们可以采取以下措施:

-合理选择布线层次和位置,避免相邻信号之间的干扰;

-使用适当的屏蔽技术,减少信号传输过程中的干扰;

-合理设置地线和电源线,减小共模噪声。

3. DDR2布线时如何优化时钟分配?

在选取DDR2布线方案中,时钟分配至关重要。可采用多种策略加以优化:

-保持时钟路径尽可能短,并保持对称性;

-减少时钟路径上的串扰和噪声;

-使用合适的阻抗匹配技术,确保时钟信号的完整性。

4. DDR2布线中有哪些常见的错误?

DDR2布线过程中常见的失误包括信号干扰、时钟振荡以及信号传递质量问题等,这些误差有可能影响系统整体性能并引发数据传输错误。

5.如何解决DDR2布线中的信号完整性问题?

为了有效改善DDR2布线中信号完整性的情况,我们可实施如下几个策略:

-使用合适的阻抗匹配技术,保证信号传输的完整性;

-优化地线和电源线的布局,减小共模噪声;

-选择合适的屏蔽技术,减少信号干扰。

6. DDR2布线中如何处理电磁兼容性问题?

在DDR2的线路设计过程中,电磁兼容性显得尤为关键。为妥善处理这一问题,可采纳如下几种对策:

-使用合适的屏蔽技术,减少信号干扰;

-避免高速信号路径与敏感器件之间的交叉。

7. DDR2布线中如何避免时序问题?

为避免DDR2布线中的时序问题,我们可以采取以下措施:

-保持信号路径尽可能短,并保持对称性;

-减少信号路径上的串扰和噪声;

-使用合适的阻抗匹配技术,确保时序信号的完整性。

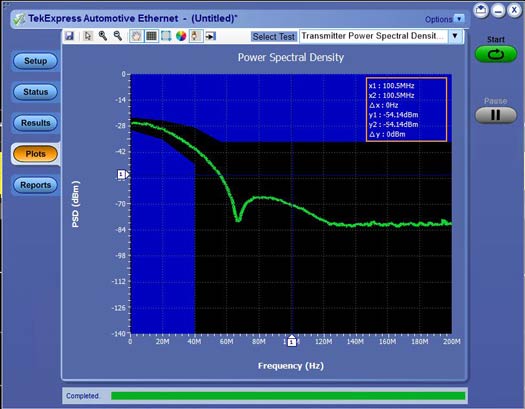

8. DDR2布线中如何进行信号仿真和分析?

在DDR2 布线中,信号仿真是一项关键技术。运用专业软件进行仿真,在此基础上评估布线效果并根据需要做出相应修正。

9. DDR2布线中如何进行延迟控制?

在DDR2布线流程中,延迟控制至关紧要。可采用如下策略实施延迟管控:

-使用合适的电源供电和地线布局,减小共模噪声;

-优化时钟路径,减少时钟偏移;

-使用合适的阻抗匹配技术,确保延迟控制的准确性。

期望上述解释能够为各位在DDR2线路设计中的困扰提供指导。若仍有疑惑,欢迎随时提问。