身为一名电子工程师,针对DDR针脚定义我有深入的钻研与掌握。DDR(Double Data Rate),这是一种高速的动态随机存取存储器技术,不仅在现代电子设备中得到了广泛采用,而且针脚定义对于其稳定运作起着决定性的作用。接下来的篇幅里,我将引领您全面了解并探索DDR针脚定义神秘的面纱,揭示其背后蕴含的复杂科技原理以及实际应用情景。

什么是DDR针脚定义?

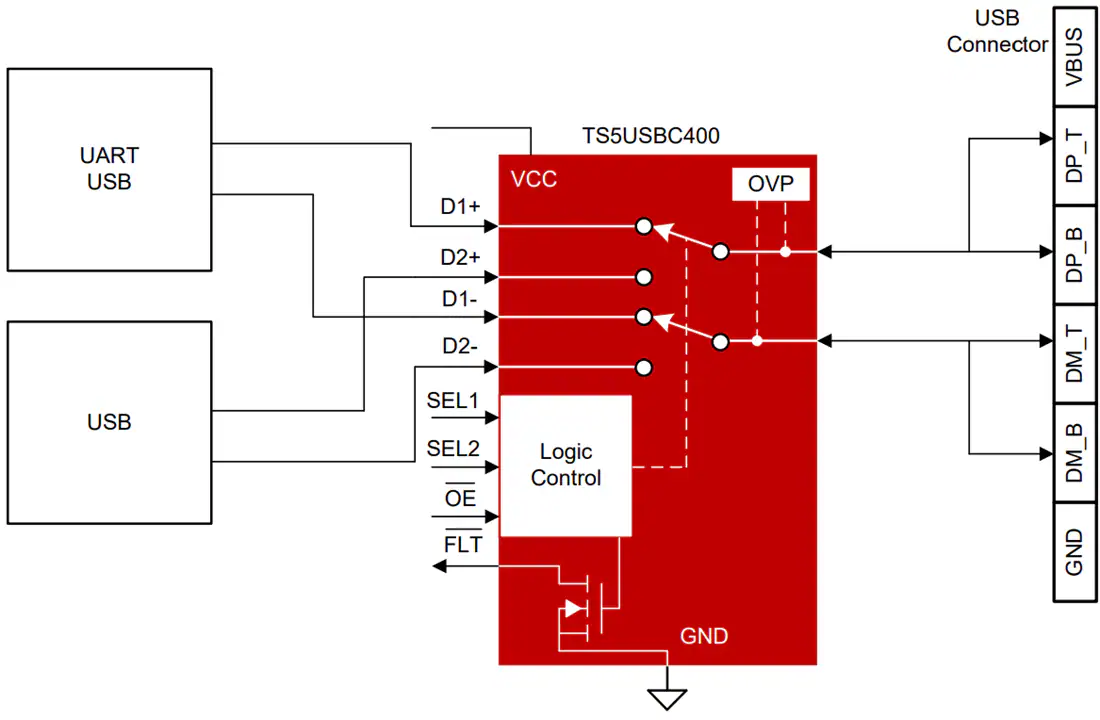

DDR引脚定义即明确DDR存储模块各引脚的实际用途及连结方式。在DDR模块内,各个引脚各自承载各种职能如数据交换、时钟信号传输及电能供给等。通过精心设计引脚功能,可保证存储装置及其它硬设备间的无误沟通,进而保障数据的平稳传送与保存。

DDR存储模组内包含数据线DQ、地址线ADDR及控制信号CS等常见引脚,每根引脚皆有其独特信号定义及电气特性。在电子产品电路板设计过程中,需精确对应连接各引脚至指定位置。对DDR针脚定义透彻理解并进行精心设置,有助于提升系统运行效能,保障数据传输的稳定与可靠。

DDR针脚定义中的主要信号

DQ数据线:此为DDR存储器关键部件之一,其主要职责为传递输入输出信号中的数据。在DDR架构中,数据线路分别命名为数据输入线路(DQI)及数据输出管线(DQO)。它们负责将存储器内储存的资料传送给处理器或者其他相关设备,同时也会收取外部设备发来的信息。

ADDR 地址线:这是内存插槽中的关键引脚,其作用在于标识内存单元或寻址硬件在存储器中的具体位置。借助该地址线,处理器快速而精确地读取/写入特定数据。在 DDR 针脚标准中,地址线的配置会针对内存的容量和寻址范围进行适应性调整,从而保证内存的有效定位及访问。

CS:控制讯号为DDR内存模组中执行读写及时序同步的重要工具之一。此信号可协助处理器下达读写命今至记忆体,同时操控数据传输起始与终点。DDR的针脚定义里,常包含时钟电平、写激活、读激活等讯号,以确保预设的数据传输顺利施行。

如何正确配置DDR针脚定义?

妥善设定DDR针脚定义对系统架构与硬件衔接至为关键,以下流程关键点须明晰。

深研规格书:首要任务是熟读DDR存储模块的规格说明书,精准掌握各引脚职能及其电气性能需求。规格书内常包含引脚排布图表、引脚功能说明表以及时序图等详尽信息。

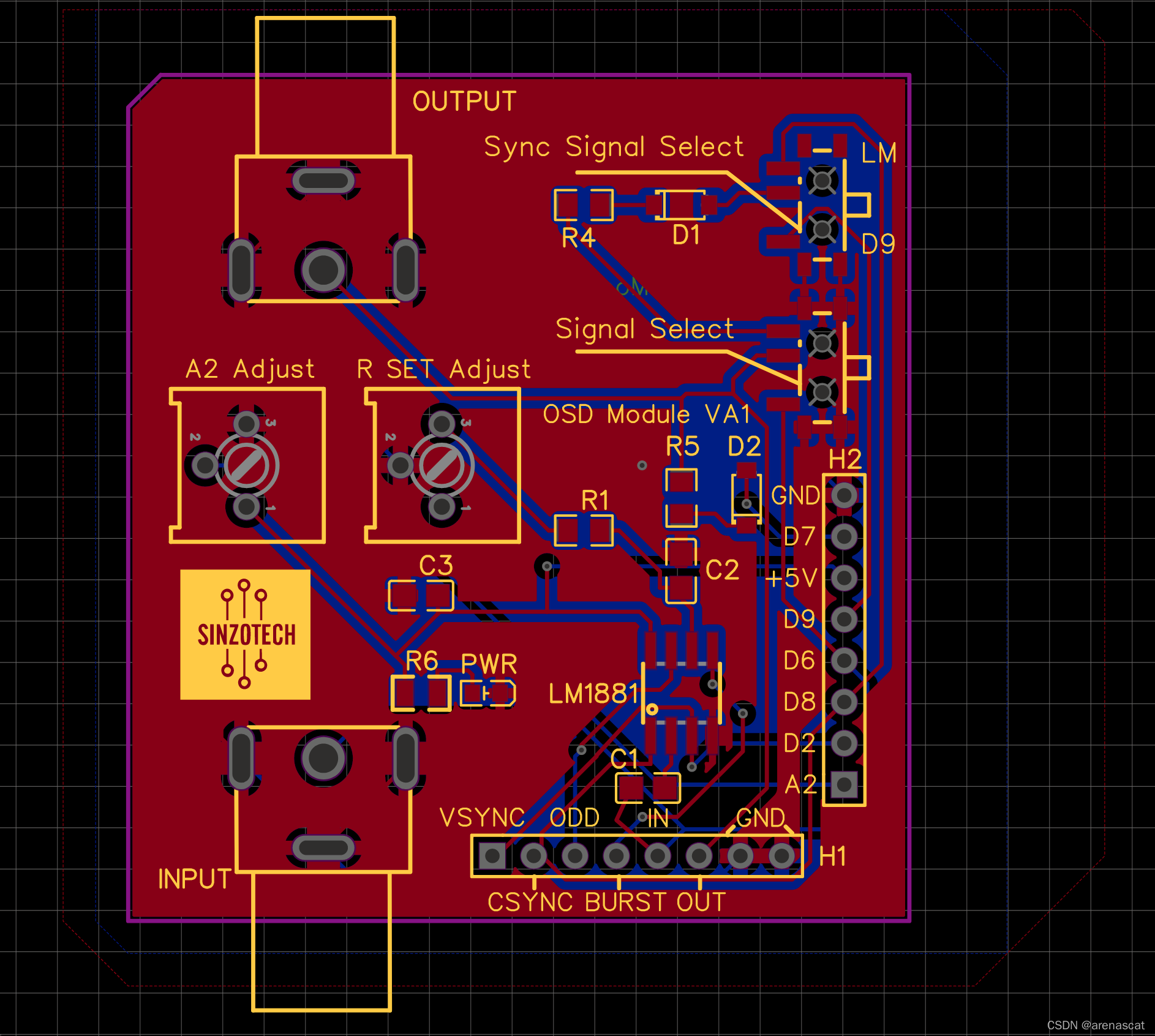

设计电路图:从规格书获取关键信息,构建全面精确的DDR连接电路图,涵盖对处理器和其他外设的引线连接以及电平转化等核心内容。

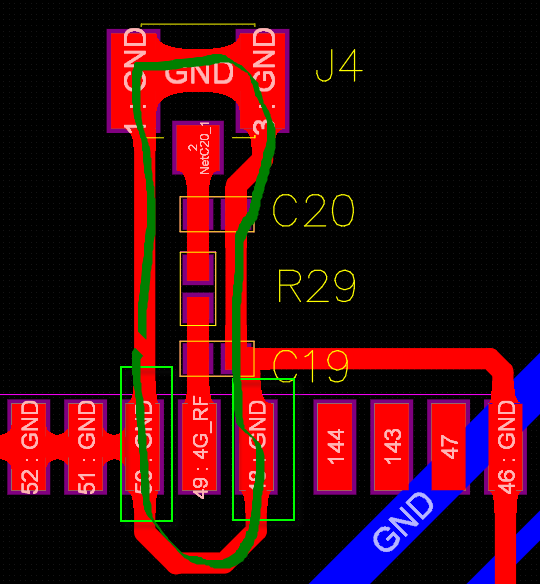

PCB布线规划:依据DDR引脚界定,悉心安排各接口的布局位置,以规避可能出现的电磁干扰及接地回路等问题。

信号完整性的严格检验:在硬件创作完工之后,有必要进行严谨的信号完整性检验和深入的仿真模拟,以保证各组件之间的引脚联系与时序要求相符,且无信号串扰或反射等现象。

DDR针脚定义与系统性能优化

恰当的DDR针脚设置可确保系统稳定运行并提升其性能。

精准定时:通过精密调整时钟与控制信号的时间序列来确保稳定性并最大化提升数据传输效率。

节能降耗:借助供电引脚与地引脚的科学配接,能够有效降低电路消耗,防止系统过热现象发生。

抗扰性提升:经过精心布局调整的系统具备更强的抗干扰能力,降低了外界环境条件对数据传输的不良影响。

DDR针脚定义未来发展趋势

伴随着科技持续革新与市场需求日益扩大,预计DDR引脚的未来演变趋势将呈现出如下特点:

高密度集成趋势:在未来的技术发展中,DDR有望向密度更高的集成模式迈进,以达到更大容量内存储器且保持出色性能稳定的目标。

高效能低能耗:鉴于节能环保理念日益深植人心,高效能低能耗的DDR产品有望得以开发,以满足环境保护之需。

多样化发展:随着技术的不断进步,我们将有望看到更多具备多种功能集成于一身的DDR产品问世,从而更好地满足各类应用场景需求并显著提高系统整体性能表现。