近年来,本人专注于FPGA在DDR3控制领域的理论与实证研究,收获颇丰。本文将浅析个人在此过程中的心得体会,并为同行提供指导性建议。

1.了解DDR3基本原理

要精准掌控DDR3性能,首要原理解析至关重要。需透彻认识时钟信号、数据线、地址线及控制信号在系统中的功能及其链接方式。唯有深刻理解DDR3内部运作程式,方可实现高效操控与优化。

2.熟悉FPGA芯片规格

不同厂牌所产FPGA芯对于DDR3之操作机制或有区别。故在设计之始,务须详读相关FPGA规格之手册,明了其支持特性及潜在限制。

3.调试时注意时序

DDR3接口对时序要求甚高,一旦出现时序问题极易误传数据。为此,我们必须在调试过程中细致侦查并调整时序参数以保证数据传送无误。

4.优化信号布线

优秀的信号布局是确保DDR3控制稳定可靠的核心要素。在布置线路时,需尽可能缩短信号线,降低其长度及交叉干扰;同时,科学安排电源与地线的走势至关重要。

5.合理分配资源

对于FPGA操控DDR3的设计,务必审慎分配FPGA资源,使其各司其职。将各项功能元件分别归置至相应的逻辑单元内,以尽量发挥FPGA芯片的性能潜力及资源配置能力。

6.使用合适的时钟频率

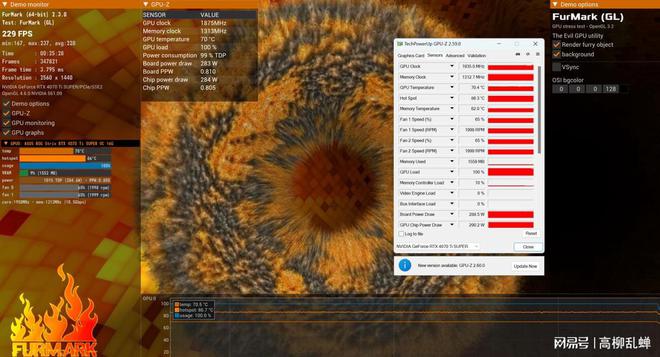

选定适宜的DDR3时钟频率尤为关键,它直接决定了数据传输的准确性与性能。经过深入探讨与实证分析,我们可以定出理想的时钟频率设定值。

7.进行严格的验证测试

为确保DDR3控制器设计稳定性与可靠性,必须进行全方位严谨验证测试,诸如读写功能测试、时序分析等环节必不可少。

8.注意电源供电

DDR3存储器对电源需求较高,为了保证其正常运行,应强调电源供电系统与稳压器的稳定性。在设计过程中应关注这一部分,采取有效的电源滤波和稳压操作。

9.注意信号完整性

确保DDR3信号完整性的关键在于保障数据传输的稳定与可靠,其核心策略是优化PCB布线并选用适宜的阻抗与终端电阻。

10.持续学习和实践

在FPGA操控DDR3领域,技术日益更迭,挑战亦随时涌现,故需坚持学习新知与实践操作,同时积极分享宝贵经验以提升自我能力。

衷心期望我的经验与技能分享能给正在FPGA控制DDR3技术领域中努力奋斗的同行们提供助力。面对这一领域所带来的各种问题与机遇,不断学习、实践并勇于创新,我们一定能实现耀眼的成果。