DDR3走线长度即为设计电路板时,内存控制器与存储芯片间的有效距离。在DDR3内存模组内,必须倚赖一系列的线路及接驳器来实现数据信号的传输。正是这些线路的长度直接关系到模组稳定性和效能的优劣。反之,科学地掌控DDR3走线长度便成为了确保内存模组正常运转的核心要点之一。

在实际设计过程中,DDR3走线长度受到多种因素制约,如电路板物理限制、布线,同时也关乎到信号传输速度、时序参数和信号完整性的协调。对DDR3走线长度进行精细调控,可降低信号传输延时,提高数据传输效率,有效消除信号干扰与时序偏移状况,从而显著提升内存模组的总体性能表现。

影响DDR3走线长度的因素

信号处理效率:鉴于DDR3内存凭借其高频工作状态及快速信号传输所带来的优势,我们需关注信号在布线上的传递时间,以防因过长的布线路径引起信号延迟增加并降低整体系统效能。

时序规定:DDR3内存对时序有着严格的规定,需要保证各项信号(如时钟、地址、数据)之间的时间限制。为了满足这一要求,必须精心设定走线长度,以便使数据在预定时间内抵达目的端并得到正确处理。

信号完整性:布线长度的不当会引发诸如信号反射与串扰等信号完整性问题。因此,DDR3内存模块设计需全盘考虑诸如此类影响因素,确保信号传输过程无虞受扰。

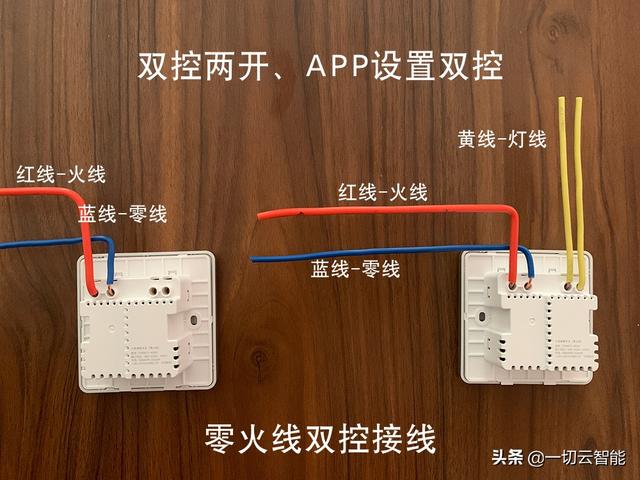

实体布置:电路板的具体摆放方式同样对DDR3布线长度有着显著影响。通过精心设计内存模组各部分元素间的间距及链接格式,我们能够有效地控制布线长度,从而增强系统稳定性。

如何优化DDR3走线长度

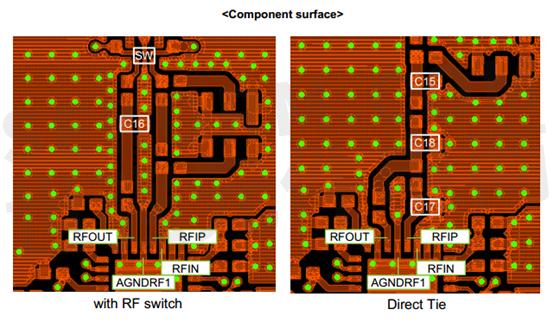

差分对:作为DDR3内存的主要传输模式,差分对的应用可大幅降低信号串扰并提高系统稳定性与性能。其核心原理在于有效缩短走线长度,进而全面增强系统整体效能。

拓扑优化:选择适宜电路板拓扑是优化DDR3走线长度的关键策略。通过适配层间堆积、布线规律与引脚排布等策略,能有效控制信号路径长度及减小延迟。

仿真验证:在实务设计过程中,可借助仿真软件来全面审视和测试DDR3内存模组,以公正客观地评价实际走线策略优劣,分析并定位可能存在的问题点,进而进行有针对性的修正与完善。

时序分析:精确且深入的时序分析乃是保障DDR3内存健康运作的重要环节。通过精确获取并分析多种信号间的时间关联,我们能依实际情境调整布线及接线方案,从而使系统在稳定状态下运行。

结语

总而言之,投资DDR3走线长对内存模块设计而言极端关键。精准并巧妙调整其长度势必对整个系统的运行效率、稳定性以及可靠性大有裨益,尤其在高速数据传送方面展现出极其重要的价值。展望未来,伴随着技术的持续演进,探索更具前瞻性的设计方法与科技工艺无疑将成为我们满足日趋复杂且高速运转的电子产品需求的必要举措。