时序准则对于设计及检验动态随机存储(DDR SDRAM)至关重要。身为拥有丰富经验的资深电路设计师,在此与您分享关于时序设定的几点心得。

1.熟悉DDR SDRAM的基本原理

论述DDR SDRAM设计与验证之始,务必掌握其基理。应深入理解其数据传递手段、时钟节拍以及内部分层布局等关键要素,以便为时序约束设定提供有力参考基础。

2.准确把握数据传输速率

在DDR SDRAM的设计与测试中,数据传输速度是核心参数。对应具体需求及系统约束条件,精准控制其速度能有效防止因速差引发的运行失衡现象。

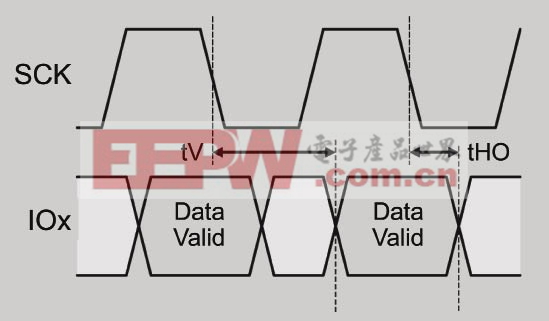

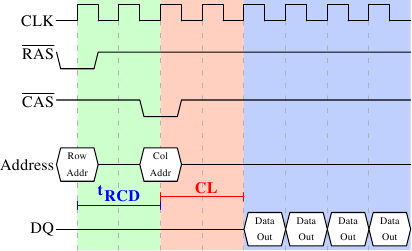

3.确定时钟频率和延迟

以DDR SDRAM参数及硬件需求为基础,合理设定时钟频率与延迟指标。此类参数直接影响着数据传输的稳定性与准确性。

4.设置读写时序

依据DDR SDRAM的技术规范与硬件环境的限制,设定适宜的读写流程。涵盖时钟信号延后、数据传递周期、阅读/写入指令执行次序等多方面因素。精确调整这些参数方可保障数据传输与处理的正确性和高效性。

5.考虑时钟和数据信号的布线

在设计阶段,布线的重要性不言而喻。对于诸如时钟及数据信号等关键部分,必须严格遵守相应规范与约束条件。合理地实施布线,有助于降低信号干扰和噪音,从而提升 DDR SDRAM 的效能。

6.进行时序分析和验证

在设计结束之后,时序分析和验证环节不可或缺。采取专业时序分析工具,对DDR SDRAM进行严谨验证,以保证其适用于各种实际环境且能正常运行。

7.注意电源和接地

DDR SDRAM性能高度依赖稳健且纯净的电源及地线,设计阶段需注重此两大系统的布局与接线。

8.参考经验与团队协作

实践证明,经验参考具有极高价值。通过团队协作,分享知识,共同处理难题,我们能够更有效地应对DDR SDRAM设计与验证过程中所面临的挑战。

身为资深电路设计师,我对 DDR 时序约束于 DDR SDRAM 的性能及稳定之影响有深刻领悟。凭借不懈学习与实战锤炼,使我专业技能日益精进,在职业道路上收获众多成就。愿这些经验传授有助于各位同仁在 DDR SDRAM 的研发与认证环节中的运用。