DDR2 DQS,这一关键性时序信号对维持DDR2内存正常运作至关重要。该信号功能在于时钟与数据同步及传输控制。本文将详述DDR2 DQS的定义、重要性及其应用须知。

1. ddr2 dqs的定义

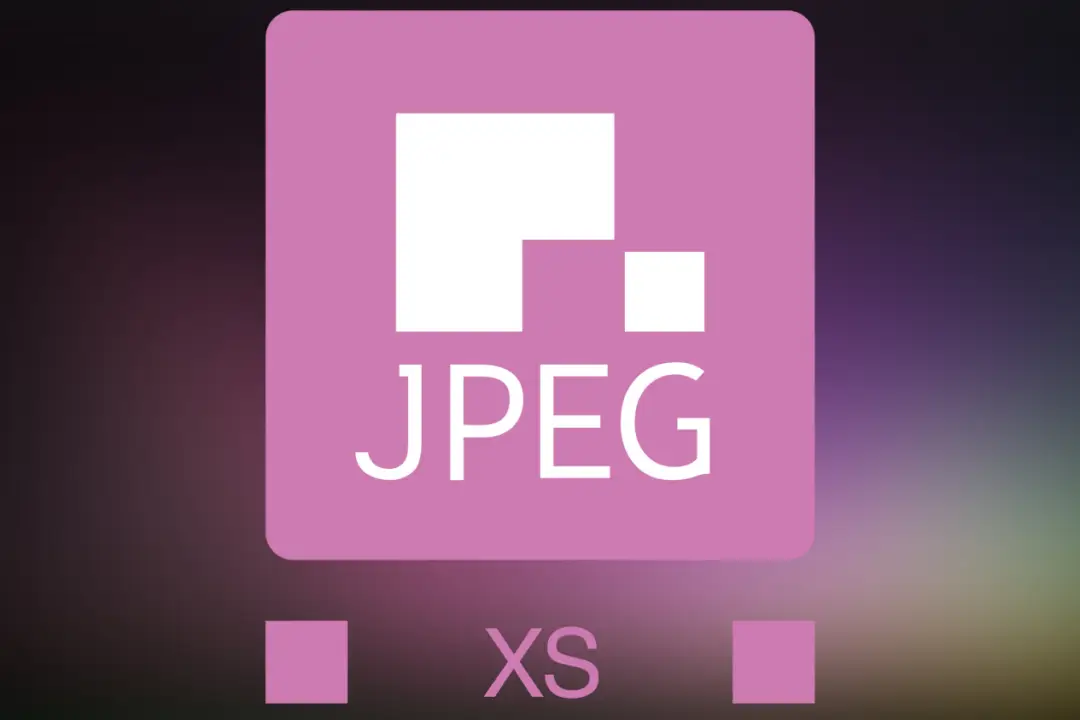

DR2 DQS即为第二代双倍数据传输率(Double Data Rate 2)记忆体内的时脉序列信号,用以监督串流数据的存取秩序。该信号由内存控制器所产生,与时钟协同运转,确保数据在读写环节能够精确传递且保持步调一致。

2. ddr2 dqs的作用

在DDR2内存中,DQS信号发挥着举足轻重的作用。它主导着数据的读/写流程,同时还要协同时钟信号,以保证数据的有效同步及储存。

3. ddr2 dqs的传输方式

DRAM2应用了差分DQS信号传输技术以减少电磁干扰并增强信号稳定度及防干扰性能。此项技术是通过数据总线来传输DQS信号,在传送过程中需同步兼顾时钟信号。

4. ddr2 dqs的注意事项

在使用DDR2内存时,需要注意以下几点:

-必须严格遵守ddr2 dqs信号时间参数的规范,以避免数据传输错误和性能下滑。

-布线设计时需着重减少DQS信号受其他信号干扰的概率,以防电磁干扰对其稳定及可靠性能产生危害。

- PCB设计时,需优化 dqs 信号布线路径,降低传输延迟与能耗,从而提升数据传输效能。

5. ddr2 dqs的优化方法

为了提高DDR2内存的性能和稳定性,可以采取以下优化方法:

-改进时钟与数字序列输入信号布局及布线设计,减少传输延迟并降低损耗

-合理设定DDR2内存時序參數,依具體應用環境調整。

-运用优质电子元器件与原材料,确保信号传输的高效可靠及稳定表现。

6. ddr2 dqs与其他时序信号的关系

在DDR2内存运作过程中,DQS信号紧密关联其他时间信号,例如CLK及DQM等,并协同工作以完成数据读取和写入。为了确保稳定性与一致性,在设计与调试阶段,必须全面把握各种时序信号间的同步与协作。

7. ddr2 dqs在DDR3和DDR4内存中的变化

在DDR技术持续革新下,DDR2内存逐步被DDR3及DDR4内存替代。针对新的内存种类,其信号定义、功能与传输方式均有更深入的调整。故而,选择及使用这几种内存时,我们应熟知且能掌握相应的时序参数以及规范标准。

通过上述七点简要阐述,想必各位对于 DDR2 DQS 有了更为深刻的认知。此信号在 DDR2 内存中的关键地位不言而喻,优化其布局与通电路径,严控时序参数,皆能提升内存性能以及稳定度。希望本篇文章对您有所启发,感谢阅读!