DDR2布线规则的重要性

DDR2为双带宽双通道动态随机存取存储器(Double Data Rate Two),此类存储设备被众多计算机系统所沿用。其中,布线规划对DDR2运维至关重要。科学的布局不仅能够提升内存运行速率与稳定性,不当的设计也易引发信号扰乱及时序失准等问题。故把握并恪守DDR2布线规制,对于保证系统运作效能极为关键。

在DDR2布线设计过程中,需全面兼顾信号完整性、时序配合以及电磁干扰等多项重要因素。首要考量的便是信号完整性,它涵盖了信号传输路径的阻抗适配及信号波形的维持与恢复等诸多层面。而在DDR2内存模块内,各类时钟信号、地址信号及数据信号均需保持高度的完整性,以保证数据传输的精准度及其稳定性。

在此次探讨中,我们关注到DDR2布线上的关键因素在于时序匹配。所谓时序匹配,即指信号传播的各阶段间的精确时间规定,以保数据准确无误地传达到规定目的地并得到顺利处理。在这种架构下,时序偏差可能引起数据误播甚至传输完全失败,结果严重。正因如此,在DDR2布线设计环节,必须注重控制信号路径的长度和时延,从而保证时序匹配的严格执行。

DDR2布线规则的具体要求

在DDR2内存模块的接线设计中,必须遵守相关的规则与要求。首先,必须尽可能缩短走线长度并确保其直连短截,以降低信号传递过程中的损失和干扰,从而增强信号完整性。

其次,为保证精准的差分对布线操作,需确保各差分对间的距离保持等长且最小化它们之间的交叉与干扰几率。否则,不等长的差分对将引起信号传送时间不协调,进而影响数据交换的速度及稳定度。

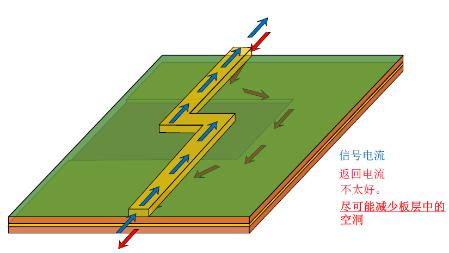

在内层布线过程中,应尽量减少90度角转折,改用圆弧布线方法,降低线阻抗变化给信号带来的负面效应。在外层布线方面,则要重点关注地与电源层间的间距及接连结构,以免电磁干扰对信号产生不利作用。

如何优化DDR2布线设计

为提高DDR2内存模块布线设计质量,可采用如仿真分析等手段。通过仿真分析工具,对各布设方案进行模拟,进而对其信号完整性与稳定度作出评估,对可能存在的问题进行提前排除及优化改善。

其次,在PCB实际设计过程中,通过利用分层布局技术,能够有效降低各信号层之间的相互干扰,增强系统稳定性。将时钟、地和电源等不同层分别规划布置,能显著减少层间干扰影响。

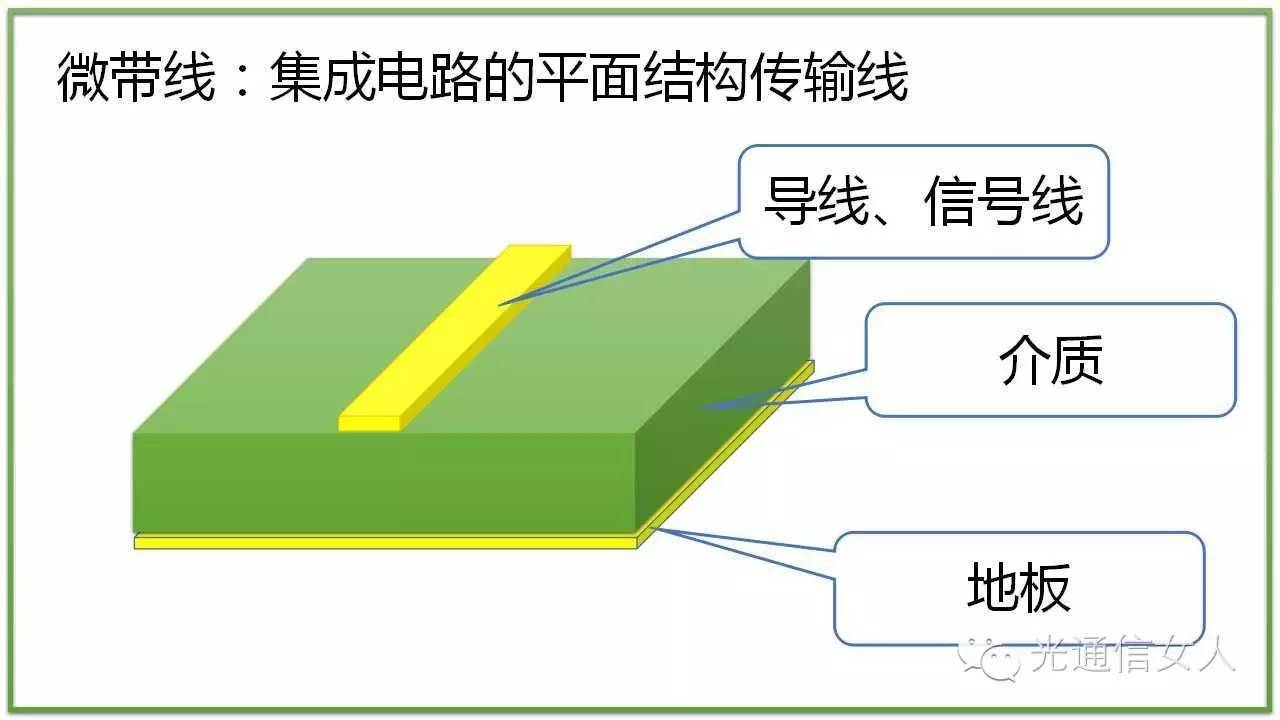

此外,为强化差分对线间效能并提升抗扰性,可运用缠绕布线法;而在内核层布线上,则适宜采用微带或同轴技术以减轻阻抗变动带来的阻碍。

总结

DDR2存储模块被视为计算机体系的核心组件,其设计过程需严谨遵守各种布线规范,以维持系统运转的流畅性与稳定性。合理且合规的DDR2布线规划有助于显著减低系统崩溃风险,提升数据传输效率,同时为整个系统的长期稳固运作提供有力保障。

在实际应用领域,技术人员需深入了解DDR2布线规范的基本理论,并在设计过程中予以灵活运用。唯有不断积累经验,将所得知识应用于实际操作之中,方能提高技术实力并提升产品素质。

期望读者阅读本篇文章后能够深化对DDR2布线规范的理解,并将所学运用到实际工作中去。