DDR3电路图的基本概念

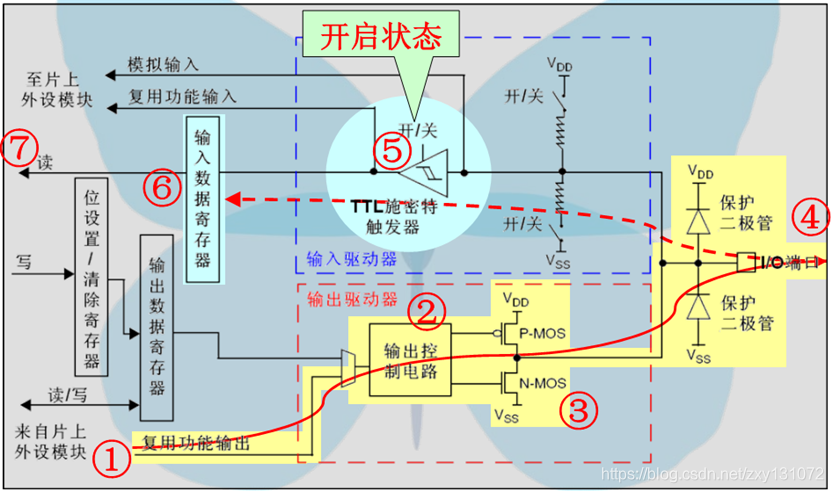

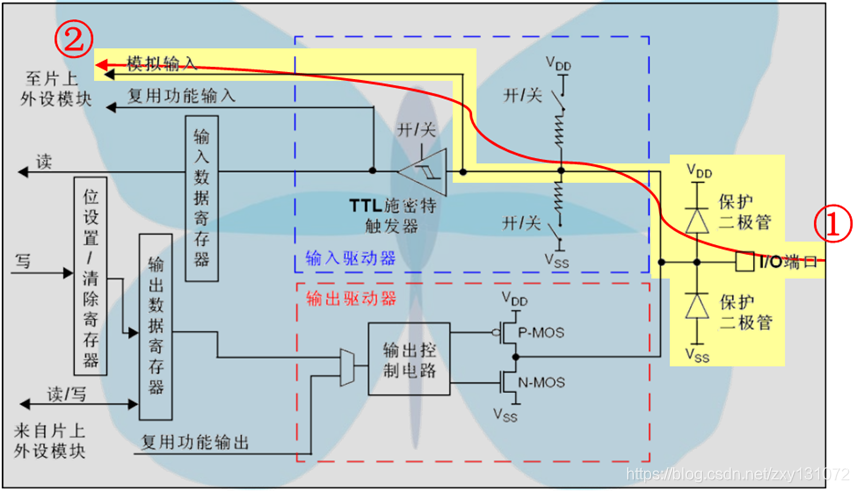

DDR3作为一款双倍数据速率的动态随机存取存储器(DRAM),在各类电子设备中发挥着核心作用。深入剖析DDR3电路图中的关键元素,是理解其运作机制与性能表现的基础。此电路图由存储单元、控制信号线及时钟信号线三大关键要素组成。其中,存储单元承担存储数据的重任,而控制信号线则负责数据的读写操作调控,时钟信号线则致力于数据传输的精准同步。

在DDR3的电路图上明确定义有地址线与数据线,前者确认存储单元的具体位置,后者则负责传输真正有价值的数据信息。各环节紧密联系,共同构成DDR3强大的内部电路系统,为高效而优质的数据读写服务提供保障,从而推动整个系统性能的提升。

DDR3电路图中的关键参数

在制定DDR3电路图的过程中,相关参数的设置应予以充分考虑。首当其冲的是时序参数,如时钟频率及延迟时间,它们对DDR3内部数据传输速率和稳定性产生显著影响。此外,电压参数亦需严格遵守,DDR3相应供电电压的过高或过低均会影响芯片正常运作。与此同时,还需关注信号完整性参数以及布局规划等方面的问题。

DDR3电路图设计中的常见问题

实际运用中,DDR3的电路图设计难免遭遇各种疑难问题,如布局设计中的信号干扰、电源噪音等,皆需借助适当的布局调节与完善的接地体系得以应对;同样,调试过程中出现的时序不稳、读取写入失误等状况,也可以透过波形分析以及使用逻辑分析仪等技术手段来精确定位并予以修复。

必须考虑DDR3电路图各厂家芯片间的适配性及稳定度,以保证全系统的功能正常运作。因此,实践中需持续针对电路图进行优化与调控,以符合系统性能及稳健要求。

未来发展趋势与展望

在科技飞速进步的推动下,DDR3这一传统存储设备正逐步被新世代技术所替代。而鉴于5G与人工智能等创新技术的迅速崛起及其对存储性能及容量的更高期待,未来存储器技术将朝向高带宽、大容量以及低功耗的趋势转变。

与此同时,DDR3电路图设计领域或将直面诸多挑战与机会。在高速通信行业,信号完整性和时序优化的需求有增无减;AI(人工智能)世界下,对大容量存储及高效运算能力的需求日益迫切;而物联网上的智慧城市建设将催生低功耗、小型化存储设备的紧迫需求等。

综合来看,作为一项传统存储技术,DDR3电路图在未来仍将发挥其关键作用。我们可对其持续进行创新优化,以开拓更为广泛的科技运用空间。