DDR内存条的基本结构

DDR内存条作为计算机内普遍使用的存储器装置,其电路结构颇为精密。该款内存条主体由存贮芯片、陈列电路以及时序控制电路构成。其中,存贮芯片担负着数据资料的储存工作,而排列电路及时序控制电路则主要负责数据传输次序与及时响应时机的调配。

在DDR内存条的电路设计结构中,最关键且繁杂的部分便是储存器芯片部分。此部分由众多存储单元组建而成,每一个单元内部均含有读取写入电路、地址解码器以及数据线路等多种元素。它们透过精密严谨的联接手法形成有机整体,构建起内存条强大的数据存储与传输机制。

DDR内存条的数据传输原理

DDR内存通过精密电路设计实现了高速数据传送。当CPU发出读写指令给内存控制器后,后者会启动特定的排布线路与时间顺序控制电路来完成这一操作。

排序逻辑负责将CPU传送之数据以有序方式组合,从而使每组数据能够有效读取或者写入。同时,时序调控电路通过预先设定的时间信号,使各个模块协同运作,进一步提升了数据传输的稳定性及安全性。

DDR内存条的主频与频率调整

DDR内存运作期间需依实际需求调整主频与频率。其中,主频即内存实际运行的时钟频率,对数据传递速率产生关键性影响;而频率则为主频信号经倍频处理后所得终极工作频率。

通过微调主频与频率,有助于提升内存条效能,但务必确保稳定运行,防止信号干扰及数据丢失等现象发生。

DDR内存条的功耗管理

在构建DDR内存条电路模型过程中,节能扮演了重要角色。鉴于DDR内存条在高速运行状态下会散发出极高的温度,故必须精心设计高效的散热系统以维持其正常运作。

除此之外,在实际运用过程中,节能减排亦是必需关注的重点。精心调整电路布局以及调控方式,有助于显著降低DDR存储器条的能源消耗,进一步提升其耐用性。

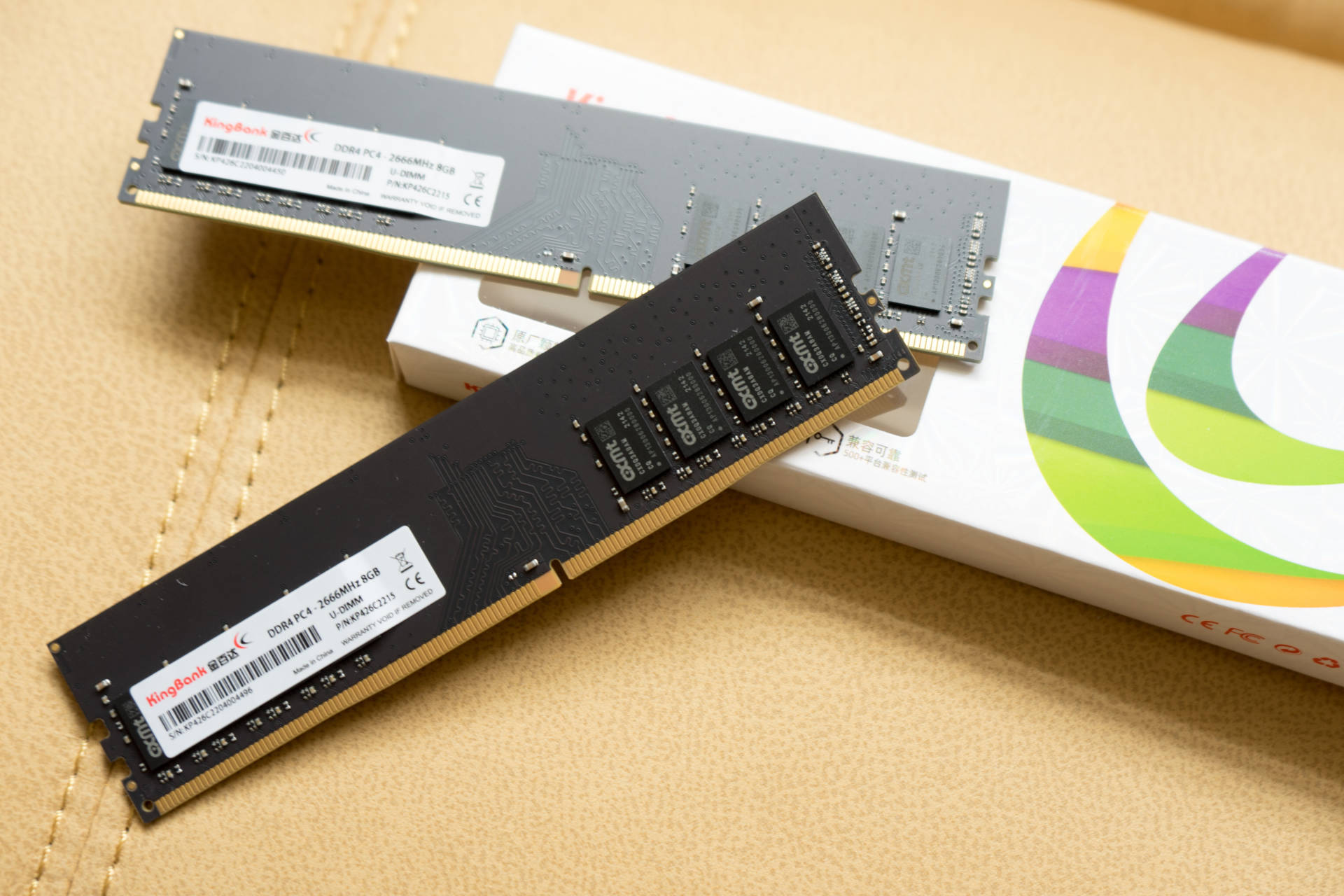

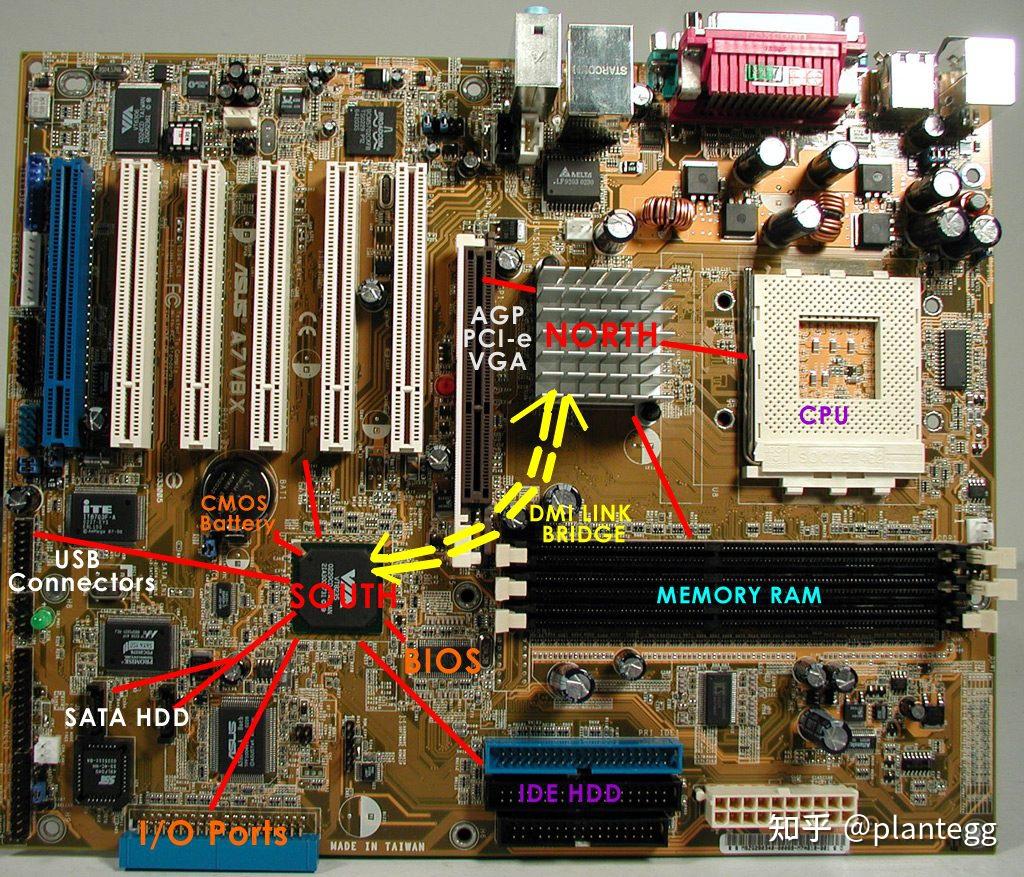

DDR内存条与主板接口

DDR内存模块需通过接口与主板相连,而电路图设计则需注重接口的兼容性及稳定性。常见的接口型式包括 DIMM 与 SO-DIMM 两大类,根据其板卡插槽类型调配使用。

接口连结处设计需关注信号传输速率、阻抗匹配及插拔可靠性等要素,保证DDR内存条与主板通讯正常且实现高效稳连的数据交互。

DDR3与DDR4内存条电路图对比

随着科技进步,DDR3已逐渐被高级的DDR4所取代。二者在电路设计上存在显著区别,如供电模式、排布顺序和时间序列调控等多个层面均有别致之处。

DDR4较之DDR3在功耗控制及数据传输速率上均有所突破,电路设计更为精密深入,采用先进科技与优质素材,以提高整体性能及其稳定性。

未来DDR内存条发展趋势展望

在科技飞速发展与需求持续攀升的环境下,未来的DDR内存条将向高速度、大存储容量及低能耗方向突破。新版本的DDR标准将陆续出台,助力计算机硬件不断演进。

在此背景下,未来发展将进一步重视环境保护与可持续性。在性能提升的过程中,必须关注节能减排。而将来的DDR内存条,有望进入更智能、集约化及逐步实现自动化生产阶段。