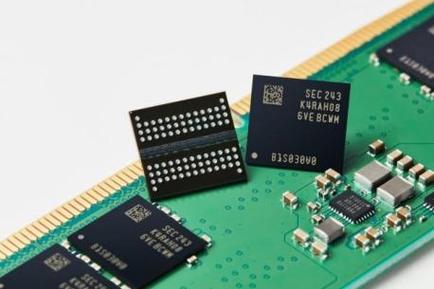

DDR PCB Layout的重要性

现代高科技电子产品中,DDR(双倍速率)内存已成为各类计算机及嵌入式系统中的关键部件。其PCB Layout设计是整个环节中极为重要的部分,对机器性能、稳健性以及耐用度表现有着显著影响。理想状态下,优秀的DDR PCB Layout不仅有助于降低信号干扰、优化时间关系,还可大大减低能耗,增强整机效能。因此,电子工程师和硬件设计师需要掌握和精通这方面的相关知识。

DDR PCB Layout设计原则

进行高效DDR PCB Layout设计,需遵循六项基准则确保障碍系统之稳定性及效能。首要原则为合理规划地线及电源线,良好的地线规划有助于减少信号环路及干扰,稳固的电源分布提供稳频电源支持。其次,认真处理时钟线路,避免与其他线路混绕并维持长度平衡,确保精密时序无误。再者,务必科学布置差分对信号线,确保高质量数据传输无虞。

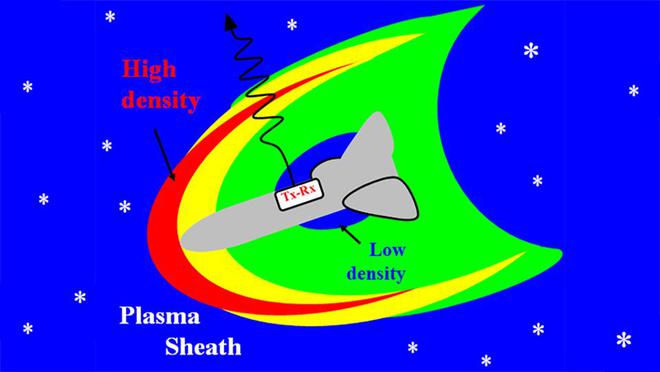

在DDR PCB设计过程中,需要充分考虑地形层与电磁兼容性的影响。精心布局地形层能极大地缩短地回流路径,缩小信号环路面积;展开电磁兼容性研究要避免信号间的相互影响,消减辐射噪声,还要采用必要的屏蔽手段确保系统稳定运行。

DDR PCB Layout布局技巧

在实战DDR PCB布局作业时,操作者需掌握若干秘诀与实践经验。首当其冲,选材时需考量介电常数与损耗因子等指标,确保满足高速信号传递要求。紧接着,应力求缩短布线长度、削弱走线阻抗,及防止各类导致信号频率损失的情境,如盲孔或盲槽等。同时,亦需合理规划元器件与通孔位置,预留充裕空间以利散热与电磁屏蔽之用。

差分对布局优化

差分对是DDR接口普遍应用的信号传输模式,连接质量对于数据传输有着决定性影响。在布局差分对线路时,必须确保两根线缆之间距离相等,保持一致的匹配长度以免产生信号失真。其次,在跨越层次转变处应利用合适的拐角方式来减少信号反射;在此过程中,务必监控和调整线宽以及间距等参数以符合设计标准。

时序匹配与延迟控制

在DDR系统设计的重点环节中,时序匹配与延迟控制尤为关键。通过精确调整各信号传输路径的距离以及引入适当的延迟线技术,可实现正确无误的数据同步。与此同时,在布线阶段需充分考虑各数据传输路径的延迟状况,采用必要手段精准调控延迟,满足系统设计所需。

功耗管理与散热设计

随着计算机系统的日益强大,功耗控制与散热策略的重要性亦随之显著增强。DDR PCB Layout设计过程中,必需关注模块功耗分配状况,合理规划供电网络以确保各个组件均得以稳定供电。同时,散热设计环节中,要为散热器预留充足空间,通过科学安排通风孔、散热板等途径提升散热性能。

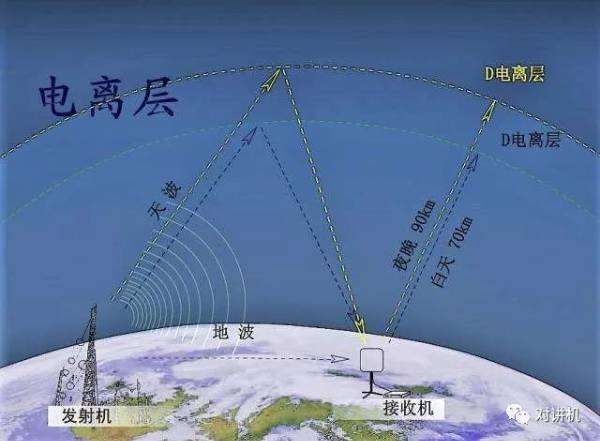

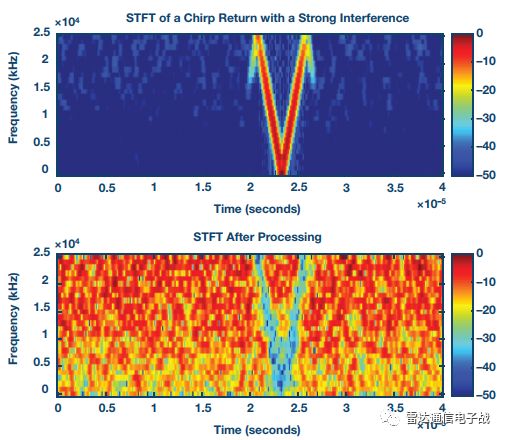

EMI/EMC设计考虑

电磁干扰(EMI)以及电磁兼容性(EMC)已成为现代电子产品设计的重要议题。在主板板材层叠的布局上,务必注重信号尖端的排列与走线路径,这将直接关系到系统辐射噪音及抗干扰能力。通过精准定格引脚位址及引入屏蔽罩等措施,能显著降低系统的辐射噪讯,提升整个系统承受外部电场环境的能力。

验证与调试

终章,DDR PCBLayout深化设计成果审查至为关键,此过程包含SI仿真以及眼图测试等核心环节,用于全面评估系统整体性能且发现潜在问题;在此基础上,注重诸如波形质量、功耗状况等具体参数的监控,以确保实体设计能完全满足预设预期需求。若确认存在问题,需要迅速采取相关措施进行修正及重新审定,直至设计符合既定标准方可宣告顺利结束。