DDR4内存简介

DDR4内存作为高效的双倍数据率型内存,系DDR3内存的改良型号。其在传输速度、节能效益及存储空间上的显著改善,使其跻身为当今主流记忆体类型之列。而DDR4内存的特有周期性序列,亦为衡量其性能发挥的至关重要的标志之一。

时序对内存性能的影响

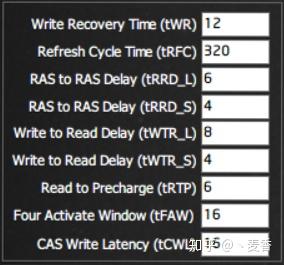

时序在内存芯片内负责操控数据读取及写入的次序与速度,对内存反应速率与稳定度具有重大影响。DDR4内存时序17代表的其实是内存模组内多个设定值,如CL、tRCD、tRP、tRAS等等,它们共同决定了内存读取操作的延迟和吞吐量等关键性性能指标。

CL(CAS Latency)- CAS延迟

CL(CAS Latency)是DDR4内存基础时序指标之一,代表接收读指令至数据起传输间的延时。该数据越小,内存反应性能越迅速。DDR4内存常有的CL值包括15、16、17等,数值17则代表每次读操作需历经十七个时钟周期方能完成。

CL设定必须在性能与稳定间求得平衡:降低其值可提高运行效率,但亦有可能引发系统异常乃至无常运作。故在选定DDR4存储器的延迟数值时,应以实际需求为依据,选取适当的CL设定。

TCRP (RAS至CAS延迟)-行态至列态的响应速度

在 DDR4 内存体系钟,另一关键时间参数为 tRCD(Row Cursor to Column Cursor Delay),这表示从提交行地址至发起列地址之间的周期数量,决定了存储器的执行速度。降低 tRCD 值,能有效减缓读写操作的延迟,进而提高存储效能。

DDR4内存中的tRCD(暂存器延迟时间)如设为17,则芯片需等待17个周期方能发送列址并执行读取操作。适当调节tRCD指标,可实现读写效能与系统稳定性之间的协调,而在超频或高性能需求情境中,则常降低此参数以提高响应速度。

tRP( Row Precharge Time,行预充时间)

TRP(Timing Reference Period,时序参考周期)为DDR4内存所控最新技术之一,用于衔接一次数据访问与下次访问间的等待时间。降低TRP值可缩减行间转换时间,从而提高读写能力和流畅性。

当DDR4内存的tRP数值处于17这个基准时,意味着前一次操作完毕后需等待17个时钟周期才可启动下一次访问。正确调整tRP值对于优化连续读写效能至关重要,尤其是面对大量数据或者要求高速吞吐的环境。

tRAS(Row Active Time)-行活动时间

在DDR4内存技术领域,tRAS参数直接影响了行活动的时长。其含义为行被激活后维持有效状态所需的时间长短,旨在确保高速准确地读取相关数据,从而提升数据传输速率与响应时间。

当DDR4内存模组将tRAS设定为17时,意味着激活行需持续保持打开状态长达17个周期方能关闭。合理调节该值有利于实现快慢兼得的反应性能及系统稳定运行,各运用领域可依据实际需求酌情调整该参数。

总结与展望

当今主流的DDR4内存在高性能运算与游戏娱乐等应用中表现出色。然而,及时序设定对系统性能及稳定有着重要影响,故在选购和配置DDR4内存模块时,务必基于实际需求和系统情况作出合适的调整。

在DDR4内存时序17的设定中,科学制定各个数值可实现其潜能最大化,从而提升整个系统的运行效率。展望未来科技的进步与演进,我们有理由期待DDR4及其他新型号将迎来更为强大且高效的时代。