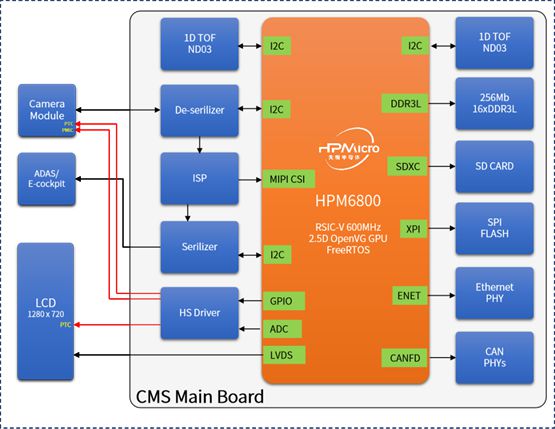

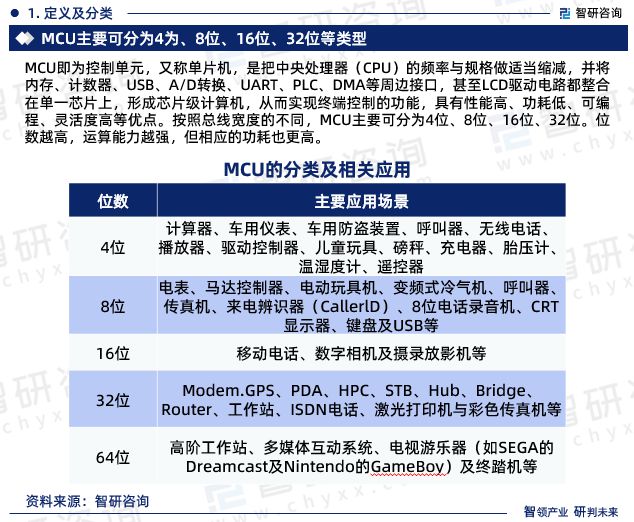

DDR3内存电路图作为计算器内存设计中的典型范例,专用于数据交换与储存。此项设计以精心布置的元件与连接为核心要素,实现了计算机高效且稳定的数据处理任务。为确保其性能最大化,应注重调整影响信号传输速度和稳定性以及功耗的各部分参数及排布。

在DDR3内存电路的设计构成中,主要包括了存储元件、地址线、数据线及控制线几个关键要素。其中,存储元件作为基础构成元素主要负责数据的储存;地址线则主要担负着指明数据具体定位的职责;数据线则专门负责实际数据内容的传输;而控制线则起到掌控数据读写操作时机与模式的关键作用。这四大组成部分相互协作,使得整套DDR3内存电路得以完美呈现。

DDR3内存电路图中的关键元件

DDR3存储器电路中的核心部件包括:时钟发生器,其精准地生成时钟信号,指导数据传送的时序;地址解码器,依据地址线上的信号精准选择指定存储单元;数据缓冲器,有效提升数据传输速率与稳定性;此外,还包括输入/输出缓冲器及写入寄存器等部分。

这些关键部件密切协作,共同保障了DDR3存贮器电路的稳定、高效运作。每种器件均担负独特职责,对整体电路起到了关键且无法代替的贡献。

DDR3内存电路图设计考虑因素

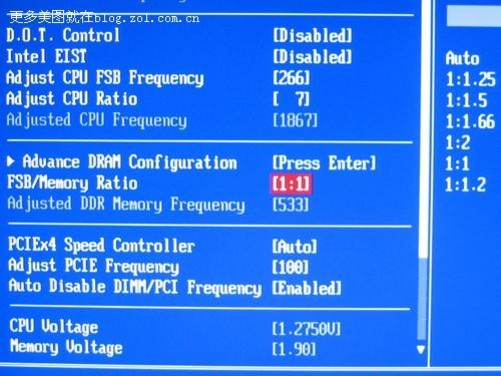

为确保DDR3内存电路图的正常运行,务必慎重考虑诸多辅助因素。首要任务在于注重信号完整性——确保信号在传输过程中的无损性及抵抗力。节能环保也是不可忽视的关键之一,需尽全力降低功耗,以便控制热量与能源消耗。紧接着便是对时序约束的严格掌控,以确保各个信号严格遵循既定时间要求。当然,电磁兼容性(EMC)以及静电释放保护(ESD)同样值得重视,均必须在设计阶段充分兼顾。

设计者需整合考量以上要素,在确保效能的同时优化各环节。唯有对诸项要素全盘兼顾,进行明智之权衡,方能缔造高效能且稳定可靠的DDR3内存电路图。

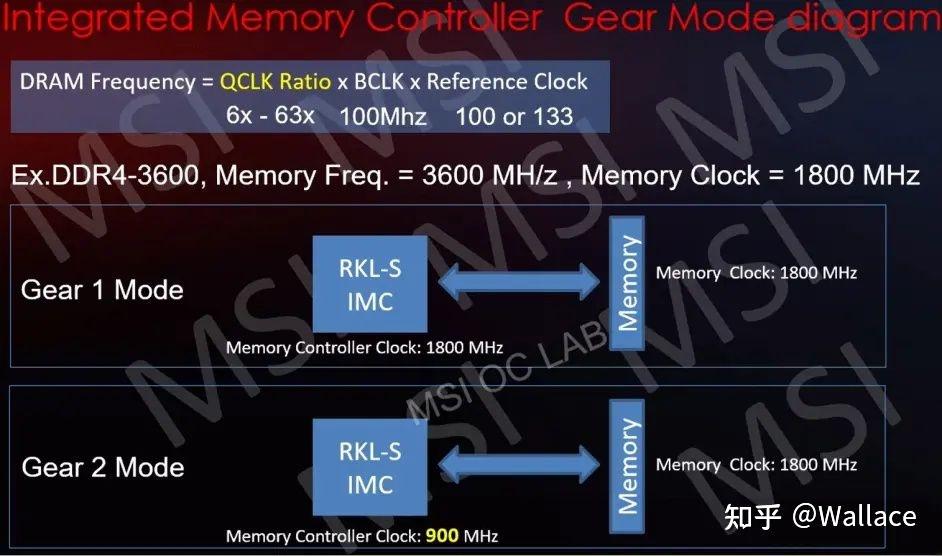

DDR3内存电路图与性能优化

实为提升DDR3内存电路图效能,实践设计过程中精准采取如下优化策略。第一项便是布局优化,通过合理配置组件与连接线路,充分缩短信号传播途径及降低串扰隐患;紧接着是供电方案精调,运用低噪授电以更有效保障系统稳定;此外不可忽视的一环即是时序优化,调整各信号线的时序以符合严苛标准。

此外,可采取选用优质元件、运用尖端工艺以及实施仿真检验等措施,全面提升DDR3存储器电路性能。此类高效策略对于提高DDR3内存单元在整个计算机系统的运行效能,乃至给予用户更为顺畅敏捷的运算体验都具有重要意义。

未来发展趋势与展望

历经科技长足发展后,DDR3内存已被高速高效的新型内存替代。然在某些特定环境中,仍需依赖此款内存模组。展望将来,新技术日益爆发之际,或许将给DDR3内存电路设计带来全新思路与活力。

在人工智能及大数据等科技飞速发展的当下,人们对计算机系统性能提出了更高要求。从这角度看,未来DDR3内存电路图设计与应用的相关研究将日益增多并产生众多创新性成果。这些新进展赋能技术进步和应用领域扩张。