什么是DDR3信号完整性

作为基础设施之一的DDR3内存,其性能优劣直接关乎电子设备的稳健运行。而DDR3信号完整性的关键就在于维持信号传输中的精准度、稳定性与可靠性,从而保正数据能够顺利地读写。为了实现这一点,诸多方面如传输线路设计、布线规范、终端阻抗适配乃至时序调控都需予以重视。

在DDR3内存中,数据经由总线交换,然而这过程受诸多因素影响如反射、串扰、时钟偏移等,可引发信号失真,从而干扰数据的精确传输。因此确保DDR3信号完整性的重要性不言而喻。

DDR3信号完整性的重要性

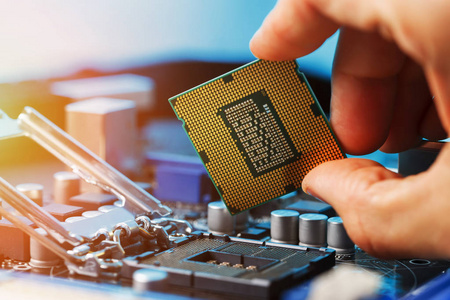

作为电脑系统重要组件之一,DDR3内存的信号质量对系统稳定及性能有着直接影响。若DDR3信号出现问题,可能造成数据丢失或系统故障,严重者甚至引起硬件损伤。因此,在布设线路板设计阶段,必须充分关注DDR3信号品质这个核心要素。

确保DDR3信号完整性可显著增强系统的可靠性与稳定性,有效降低数据传输过程中的误码率,进而优化整体效率。尤其面对高频数据交换需求的场合,如大规模数据库服务器、图形处理单元等环境,DDR3信号完整性表现尤为关键。

DDR3信号完整性分析方法

为了确保DDR3信号的完整性,必须采取一系列严谨的分析及测试流程。以下列举几种常见的分析方法:

时序调控:精准计量与分析时序,确保数据于恰当之时传送至指定设施。

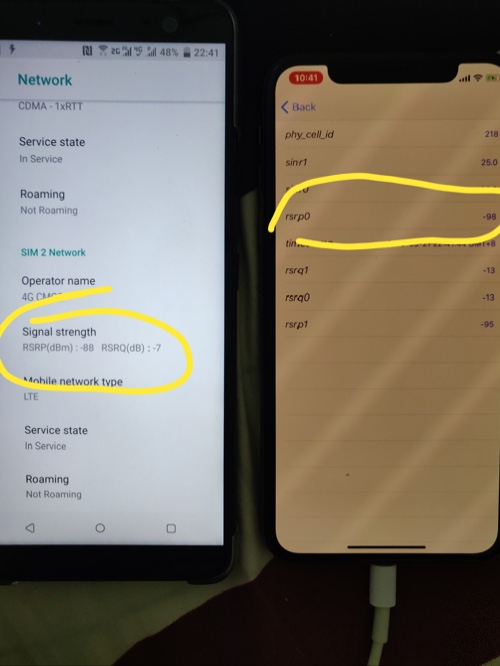

眼图分析:运用眼图检测以评估信号幅宽和稳定性,识别潜在的时钟偏差与串扰等缺陷。

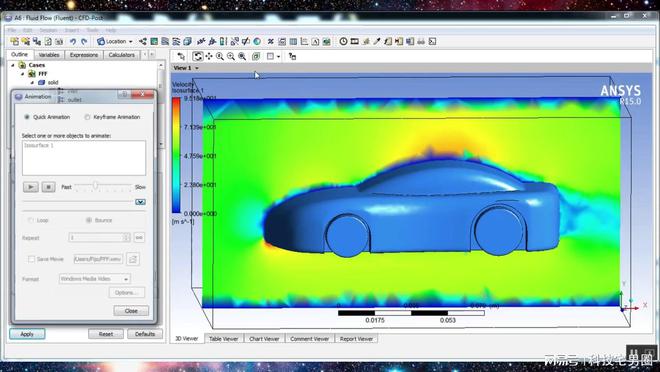

线缆建模:运用专业模拟软件构建线缆模型,进行精细化仿真实验,以揭示潜在问题并优化设计。

4.终端匹配:保证终端阻抗匹配以减少反射并提高信号质量。

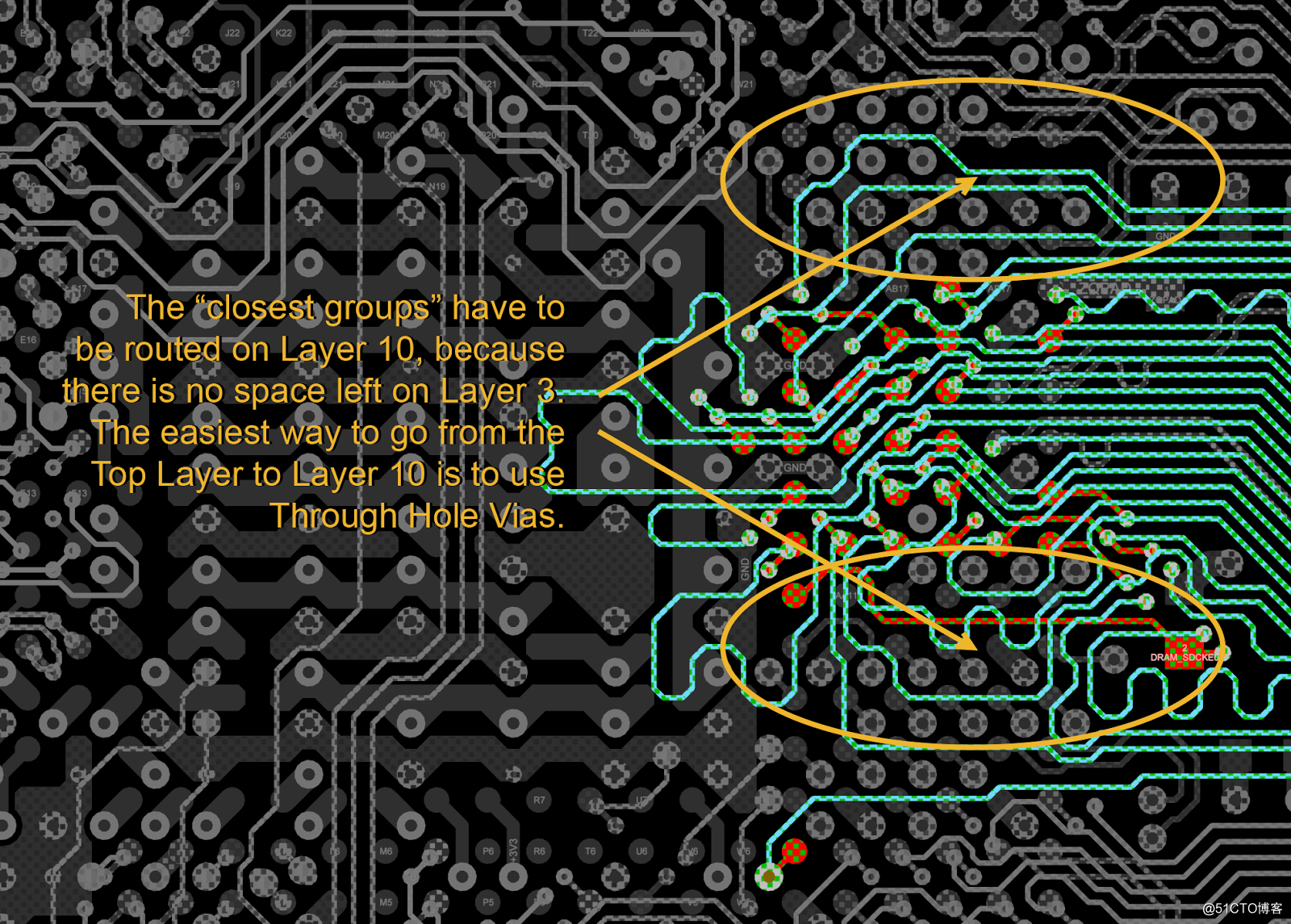

遵循布线法则:实施恰当的布线原则以降低串扰效应,深化总线稳固性。

综合运用上述手段,可全面考量DDR3信号的完整性,揭示并解决相关问题以保障系统平稳运作。

DDR3信号完整性优化策略

为提升DDR3信号完整性,在设计和布局阶段可采用如下措施:

均衡设计:确保内存模块与控制单元之间达到理想的物料空间分布,同时避免出现总线长度过度延长或者过短的情况。

电源与接地设计:力求保证电源和接地区域的大面积和连贯性,缩减电源环路面积以减少电磁干扰。

减少干扰:通过使用差分信号传输及增设防护层来减少串扰的不利影响。

终端匹配精细化:对终端电阻进行适配调整,使其与传输线特性阻抗相匹配,降低反射发生的几率。

精挑细选元器件:务必选用优质且符合作业规范之元器件,同时需关注各元器件间可能产生的干扰。

依托以上策略可显著提高DDR3内存系统信噪比得以稳定提高,从而保证整个系统性能水平的提升。