什么是DDR TCK

DDR(双倍速率数据)与TCK(时间中心内核)作为内存模块中的关键信号,负责各部件间工作流的同步,对于当代计算机体系结构而言发挥着举足轻重的作用,深刻影响着内存数据转型及稳定性。深入解读DDR TCK有助于提高本体系能效并提升运算速率。

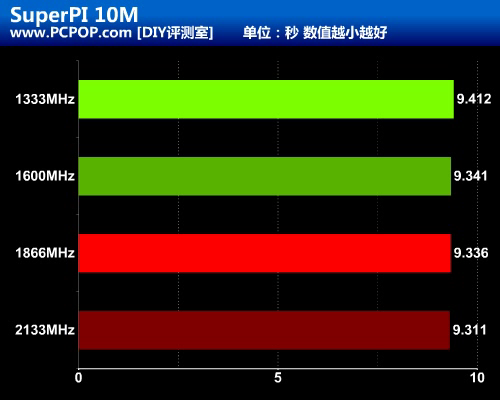

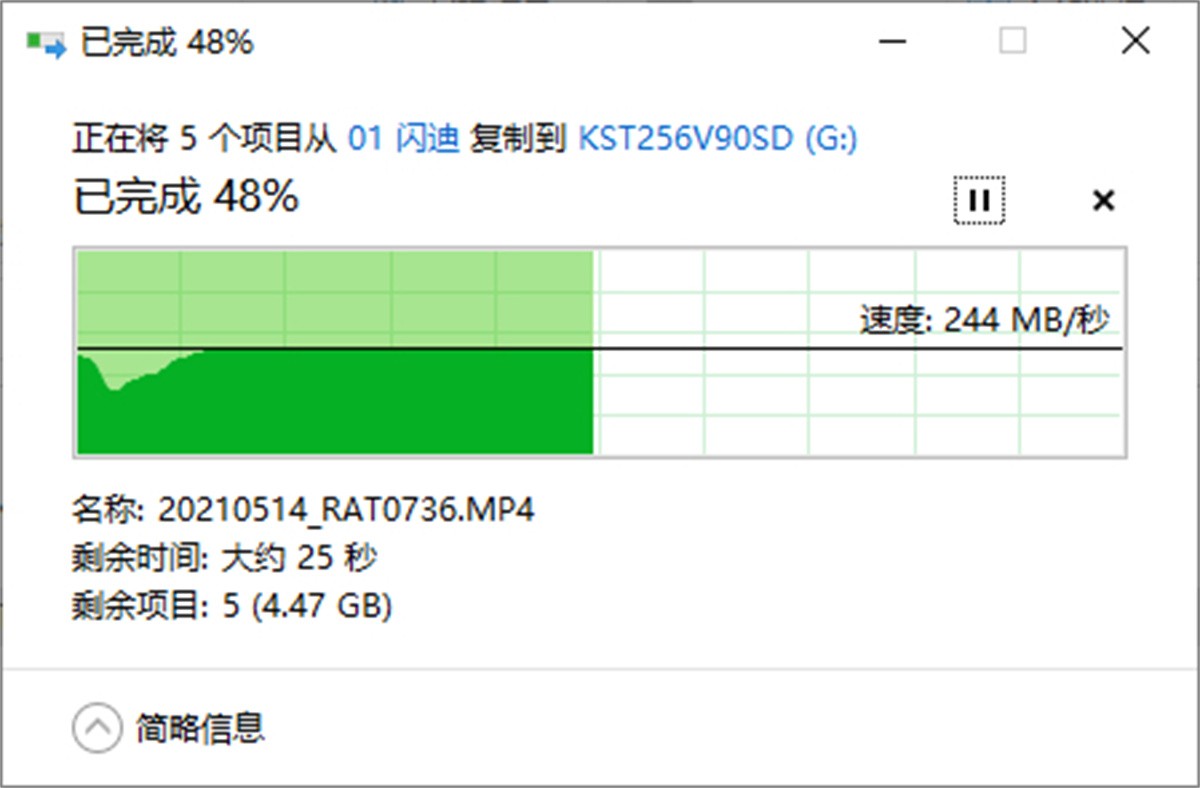

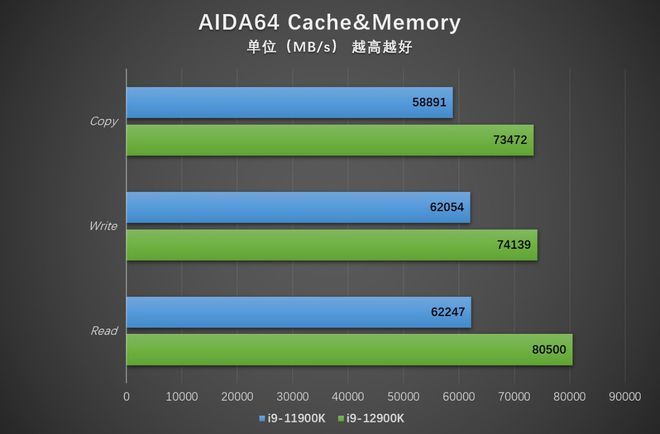

DDR TCK 频率和时序设定对内存模块的正常运作起着关键作用。其设定直接影响到主板与内存模组间的数据传输效能与精确度。适当地调整 DDR TCK频率可提升读取写入速率及数据处理效率;同时,恰当的时序参数配置也能保证数据传输的精准稳定,防止数据遗失或出错。

DDR TCK的作用

DDR TCK作为时钟信号,如同内存模块的"心脏",精准节拍掌握各部件工作节奏,以合适频率完成读写。直观来看, DDR TCK犹如指挥家,统筹内存模块内各组件有条不紊协作运作。

在实践运用中,恰当调整DDR TCK的频率可有效挖掘存储器模组的潜能。提升频次能够加速数据传输并提升系统反应速度,适度降低则有助于节能降耗以及设备保养。因此,在计算机系统的规划与优化过程中,对DDR TCK进行精细配置已成为关键要素之一。

DDR TCK与系统稳定性

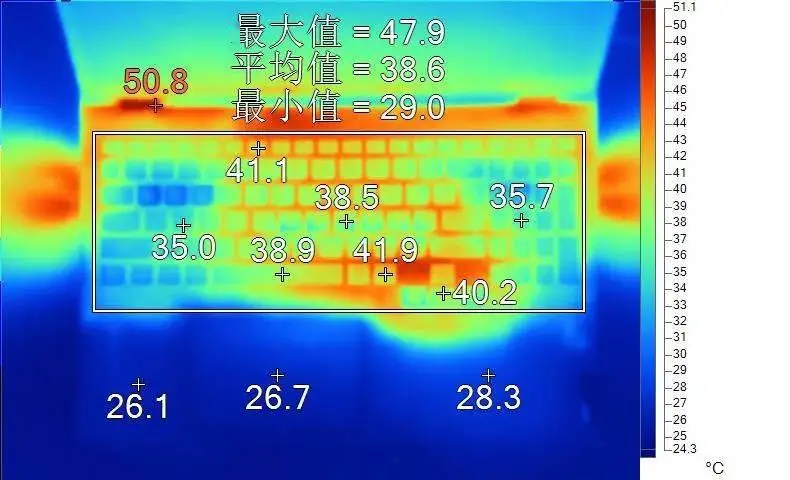

除了对系统性能产生影响以外,DDR TCK亦会直接影响系统稳定运行。过高或过低的TCK频率有可能引发内存读写错误及蓝屏等问题。因此,调整TCK频率需格外谨慎,并依据实际硬件配置和需求进行科学设定。

另外,时序参数是直接影响系统稳定运行的关键因素。若参数设定不佳,将有可能使内存控制器难以准确感知数据传输节奏,由此引发诸如数据遗失、设备崩溃等问题。因此,在调节DDR TCK时序参数时务必依据具体情况精细调整,并进行充分的性能测试,旨在确保整个系统构架的稳定运行。

如何优化DDR TCK

为最大化DDR TCK的性能,提升数据传输效率和稳定性,需从如下方向进行优化:

依性能及板卡参数设定TCK频率:参照主板及内存模组所允许之最高频率,在开机设置(BIOS)内进行相应调整与稳定性测试。

调整时序设置:参照主板制造商推荐值,或者凭个人经验进行细微调整,从而在BIOS内完成TCK时序参数的精确调节。

升级硬件配置:若无法满足现有需求,可思索更换或升级诸如主板、内存等关键部件以提升整体性能。

定期检验与维护:设备在长时间的使用过程中,硬件可能受到损坏或逐渐老化。因此需要进行定期的检查和保养,以维持系统稳定性。

未来发展趋势

科技进步与计算场景扩大催生对内存传输速度及稳定度的更高期望。就DDR TCK而言,未来出现之发展趋势可注意如下几点:

迅捷化:凭借科技日益强大及芯片制程戛然突破,DDR TCK频率将响应刷新,加速数据交换节奏。

精细化自动调优:随着人工智能技术的日益成熟,未来可能出现更加智能化与自动化的内存调控工具,使用户能更便捷地达到完美配比。

芯片整合:预见未来芯片可实现最大化集成度,如DDR TCK信号的自动化调整。

结语

本文深度剖析并解读DDR TCK这一关键理论,揭示其本质功能及运行机制,同时探讨了提升性能以及未来发展方向。故而,在整个计算机系统规划和调整过程中,DDR TCK的精确设置便显得尤为关键。