DDR PHY训练的重要性

在现代芯片设计领域,双倍速率(DDR)存储器已普遍应用于各类电子设备。为了确保其稳定高效运作,DDR PHY训练显得尤为重要。该训练主要涵盖时分秒阶段调整,信号全谐调及时钟敏感度校正等环节,旨在提升内存喷射雷达与DDR存储器间的数据转移成效。妥善且有效地进行DDR PHY训练有助于实现系统效能提升、功耗大幅下降,对产品稳定性及可靠性亦有深远影响。

为了保证DDR控制器和内存之间的稳定通信,DDR PHY训练不可或缺。该过程主要调整数据信号的时序、幅度及时钟等参数,从而保障数据准确无误的传输和处理。实际应用中,各类芯片制造商和产品均采用独立的DDR PHY训练方式和流程。因此,精通DDR PHY训练的理论知识以及实际运用对芯片设计师极为关键。

在DDR PHY训练阶段,需考量诸多要素如PCB设计、信号完整性、时序校准及噪声影响。唯有以全盘视角审视和精细优化,方能获得最理想的DDR PHY训练成果。故而在芯片设计环节,工程师必须具备深厚的电路理论基础、高超的信号处理技艺以及丰富的实际操作经验,方能从容应对纷繁复杂的DDR PHY训练问题。

DDR PHY训练流程

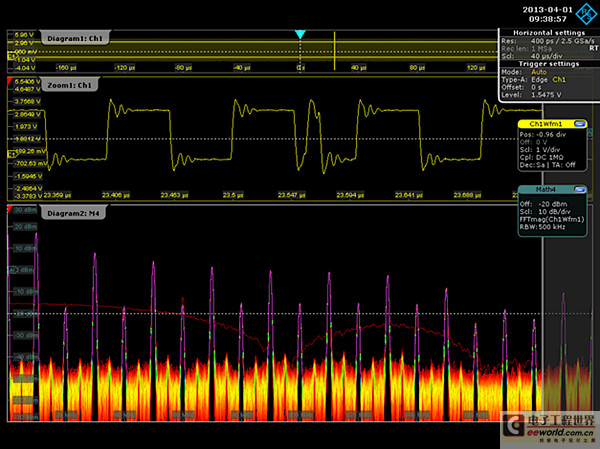

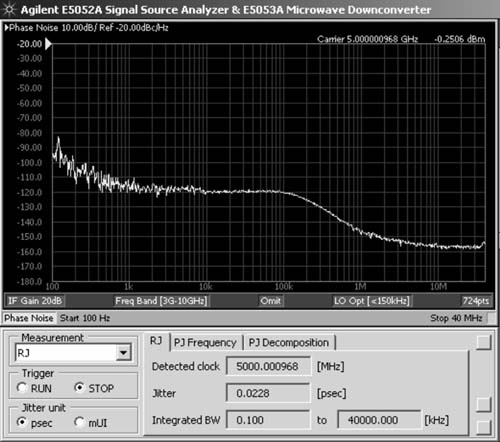

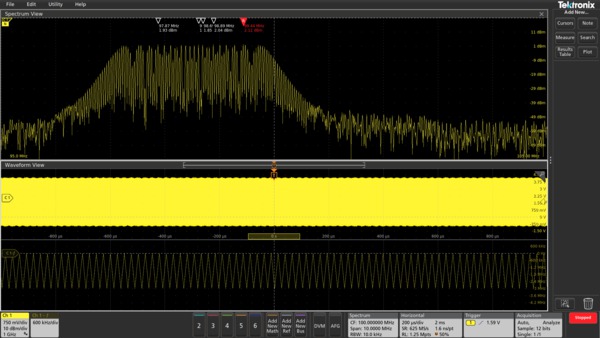

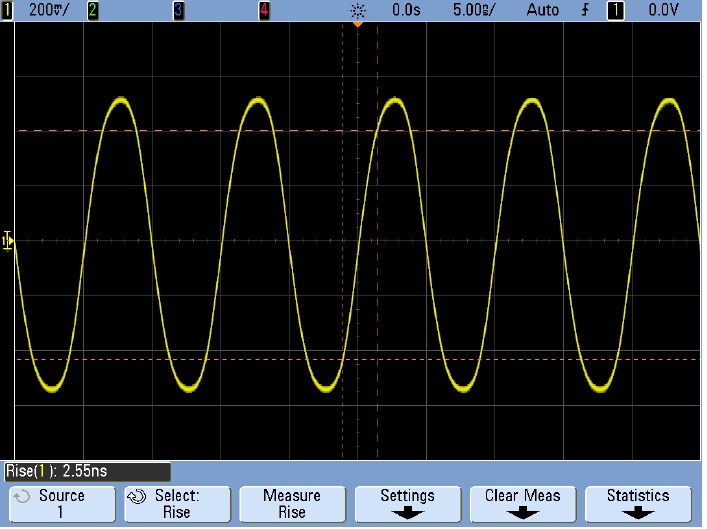

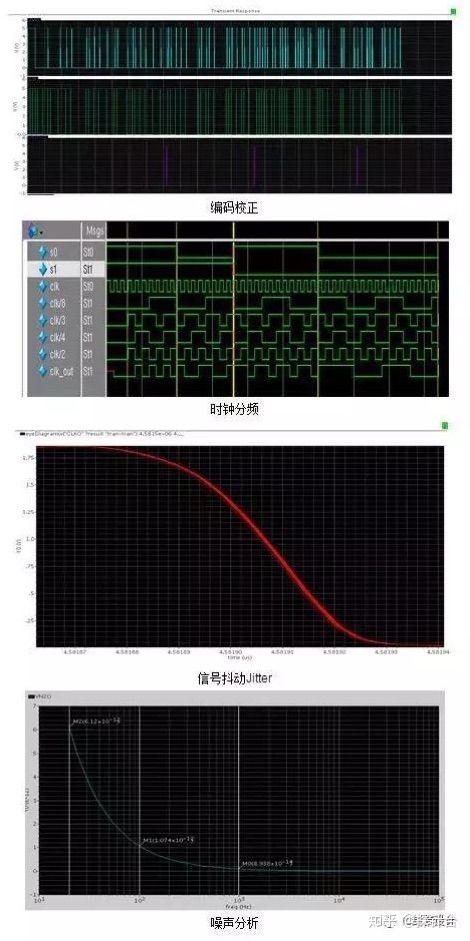

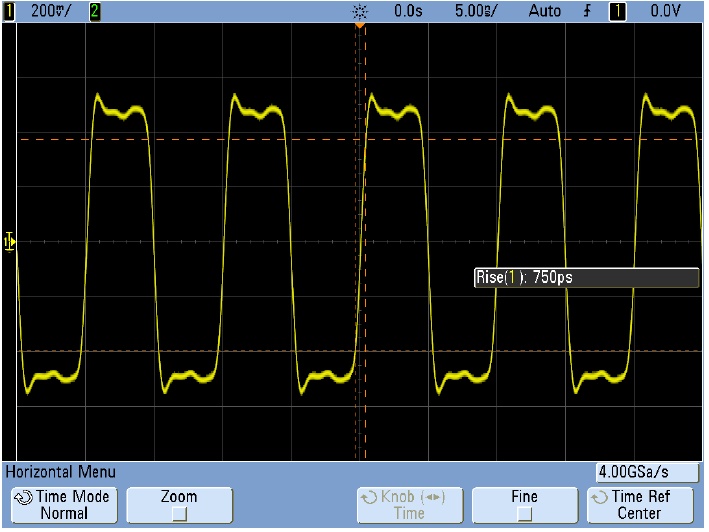

以DDR PHY训练为例,其流程可概括为四大步骤:初始化环节、时钟调准阶段、时序校准环节及数据眼图优化阶段。初始化阶段,重点任务在于建立与配置PHY基础设施;随后进入时钟调准阶段,通过精确定制时钟信号,以确保数据传输稳定;时序校准环节中,调整数据信号的延迟,进一步确保数据传输精准无误;而最终的数据眼图优化阶段,旨在提升数据信号波形品质,从而提高数据传输速度。

在各个阶段,均需执行一系列精密操作,包括发送特定编码格式、接收反馈信息及解析评估,以及调整相关参数等等。尤其应重点关注时序精准校正环节,该阶段要求对信号传输时间实现精细计量,并进行微调以确保数据准确送达至指定设备。所有这些操作皆然需要严格的技术支持,一般多须运用专用测试仪器与软件辅助。

常见问题与解决方案

在具体项目实施阶段,DDR PHY训练过程常遭遇诸多挑战。较为突出的问题涵盖时序异常引发的数据传送误差、信号完好度不当诱发的通讯失灵以及噪声干扰导致的传输品质下降等。对于此类问题,工程师将依据问题性质而实施相应对策予以有效解决。

为了解决时序不稳引起的传输失误,我们可利用延迟协调和驱动调整等技术,确保信号能准确到达目的地。对于信号完整性不佳引发的通信中断问题,改进 PCB 线路布设或添加衰减器都有助于提升信号品质。另外,对噪声污染带来的传输干扰,增设滤波器或优化地线布局是降低噪声程度的有效途径。

未来发展趋势

随着物联网及人工智能等新科技日益兴起,对存储器与控制器件间高速且可靠通信的需求大幅增加。未来,DDR PHY培训领域将涌现出诸多新颖技术及解决策略,如运用人工智能算法完善PHY参数设定和采用自适应算法提高培训效率等。此外,随着5G通讯技术广泛推广应用,实现高速且稳固的数据传输无疑将列入今后发展的重要议程。

综合各方面考虑,深入掌握DDR PHY训练的知识已然成为当今芯片设计领域至关重要的环节之一。唯有依靠不断深化的学术研究和实验操作经验,以及不断积累与总结,方能满足日趋复杂且变化频繁的电子产品市场需求和应对诸多挑战。