DDR PHY设计概述

DDR(即双倍数据传输速度)PHY,作为数字芯片与DDR存储器间的关键连接介质,其重要性不容忽视。在当今芯片设计领域,DDR PHY设计对系统性能、能耗以及稳定性具有深远影响。为实现优秀的DDR PHY设计,需全面综合考虑时序、电磁兼容及功耗优化等诸多因素,故而深刻认识并精通DDR PHY设计原理和策略具有举足轻重的意义。

在设计DDR PHY之时,应当首要理解DDR储存机制与数据传输模式,同时确保对数据时钟信号、地址信号以及控制信号在传输流程中的时序关系有深入的掌握。此外,由于存在不同频率下的时序调整需求,进行校准时序也是必不可少的步骤,旨在保证数据精确以及可靠性传输。因此,遵循实际应用情境与需求,确立适宜的PHY结构与信号调整算法是DDR PHY设计过程中至关重要的环节。

DDR PHY设计流程

DDR PHY的设计流程通常涵盖了需求解析、体系结构规划、电路构建、测验证等诸多环节。在首个阶段——需求解析过程中,确定DDR PHY的功能特性及性能参数颇为关键,这其中涉及数据传输速度、功耗设定与接口协议等方面。接下来,在体系结构规划阶段,选配适宜的PHY架构,明确各功能部件及其关联接口大致格局。进入电路构建阶段后,进一步细化电路实施方案,借助相应设备完成模拟校验、布局排线调整等事宜。在最后一个阶段,即测验证环节,针对DDR PHY的各项功能、性能进行检验,同时对照相关标准进行兼容性测试,以确保其严格遵循既定规定。

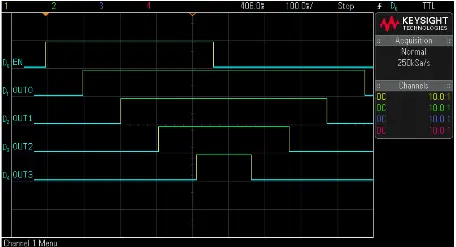

时序校准与调整

在DDR PHY开发过程中,时序校准及调整占据着关键地位。鉴于高速的数据传输特性,时序抖动可能导致数据传输错误,为了避免此类情况发生,DDR PHY采用了一种时序校准策略,该做法主要借助延迟锁相环(DLL)以及延迟线(Delay Line)等技术将时钟与数据准确同步。同时,为了适应各类工作模型和频率需求变化,时序也需进行相应的调整。

功耗优化策略

功耗优化已成为现代化芯片设计中至关重要的一环,这对于DDR PHY设计亦然。为实现更高效能的系统与更低功耗,我们可应用多种鼓励策略于DDR PHY设计期间。如选择低消耗的制程、精心调整电路和减少电源供应等技术来降低功耗;此外,以动态调节时钟频率及暂停施加功能模块等方法,对系统进行精细化功耗控制也是行之有效的办法。

EMC与SI仿真分析

在DDR PHY设计期间,要执行EMC(电磁兼容)及SI(信号完整性)的仿真测试。通过EMC仿真,可检验设备在电磁干扰环境下的耐受能力,从而揭露并处理可能存在的干扰问题。SI仿真则主要是评估信号传输时的波形畸变状况,并改善布线策略,提升信号的完整性及稳定性。

DDR PHY故障诊断与调试

在实际工程运用过程中,诸多因素均有可能引发DDR PHY发生故障或者性能显著下滑的现象。为此,进行故障诊断和调试在DDR PHY设计过程中显得尤为重要。反应迅速的故障检知系统和严密监控的功能单元相结合,既能实时监测DDR PHY的运行状况,还可即时发现并且修正故障。

未来发展趋势

随着AI、IoT等前沿科技迅猛崛起,对高性能、低功耗存储接口的需求显著增长。预期在未来DDR PHY设计中,将涌现出更为精密、高效的结构与策略;同时更加强调安全、可靠及具扩展性的诉求。故此,DDR PHY设计必将持续迈向智能化、高效化的道路。