什么是DDR上拉电阻

DDR内存中的上拉电阻对于提升数据传输速率具有关键作用。此电阻常接于输入引脚,保证在无自带驱动信号下,维持信号为高电平。此设计不仅能降低能耗,还可提升整体系统效率。

通常而言,DDR上拉电阻的取值范围有限,需要依据实际应用环境与信号需求精细调整。过大或过小均会引发信号不稳或者功率损耗过高等问题。因此,在设计数字化电路时,精准选取及设定DDR上拉电阻显得尤为关键。

此外,DDR上拉电阻在控制信号传输速率和稳定性方面有显著效用。通过适量调整上拉电阻值,可精确掌控信号的上升与下降时间,进一步提升系统整体的快速响应及可靠性。

DDR上拉电阻的作用原理

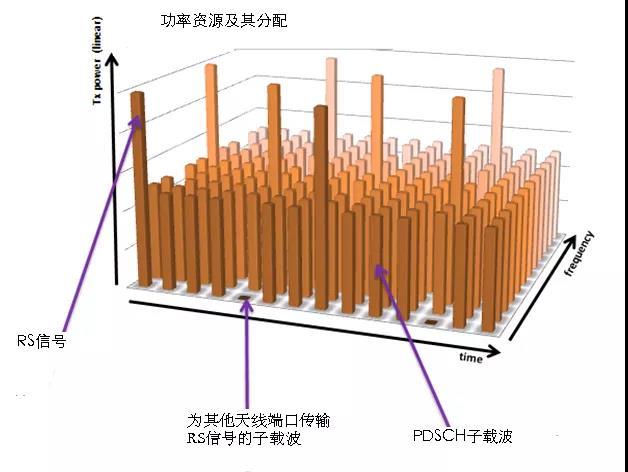

DDR上拉电阻通过将输入信号接至高电平,确保信号除非被强行拉低,否则将始终保持高位状态。若输入信号设为低电平,因有上拉电阻在内,该点将立即被抬升至高位;如输入信号设定在高电平,则对信号无任何影响。

在实践运用中,DDR上拉电阻能有效控制输入阶梯,大幅度提升系统抵抗脉冲扰动的能力。尤其是在极高频段以及超高数据速率环境下,为保证数据传输的精准及稳定,必须针对性地调整DDR上拉电阻设置。

除此之外,DDR上拉电阻还有助于降低能耗。保持输入端处在高电位以防止额外能量损失,有效提升了整个系统的能源利用效率。

如何选择合适的DDR上拉电阻

DDR上拉电阻选择对数字系统设计影响重大,需综合考量多个因素:

信号需求:基于具体应用及信号特性设定适宜的上拉电阻值区间。

抗扰性能:选用具备出色抗干扰性的DDR上拉电阻,以维系系统稳定。

能耗评估:基于系统能量消耗,慎重甄选适宜功耗等级的DDR上拉电阻。

温控适用性:充分考虑工作环境温度对DDR上拉电阻特性可能产生的影响,确保其在极端温度下亦可保持正常运作性能。

品质至上:挑选质量稳定且高性能的生产商品牌产品,同时关注其使用期限等关键指标。

恰当选择优质DDR上拉电阻可充分发挥其功效,保证数码系统稳健运行。

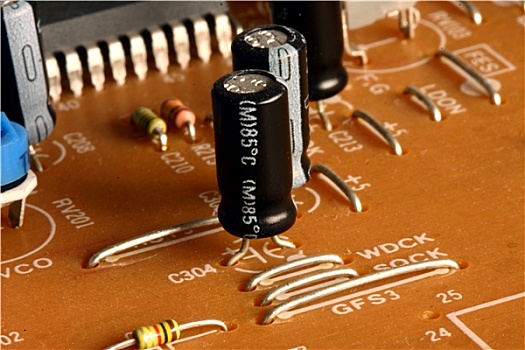

如何布局和连接DDR上拉电阻

在实际设计过程中,精确设置及妥善连接DDR上拉电阻显得尤为关键。在此,本文提供如下布局与连接方面的建议以供参考:

DDR的上拉电阻应尽可能接近芯片引脚,以此来缩短线路长度且降低干扰。

各元件间接线应短而牢固,布局秩序井然并尽可能减少交叉面积。

确保布局无共模干扰和串扰现象,力求降低噪音所致的影响。

4.注意地线与供地之间回路面积最小化。

在PCB布局阶段留出足够余地,以便于安装所选的DDR上拉电阻。

有效利用布局与连接策略可降低电路系统的噪声水平、增强防干扰性,从而使DDR上拉电阻能充分发挥其于数字系统中的关键影响。

常见问题及解决方法

在实践操作过程中,我们常会碰到与DDR上拉电阻有关的若干问题,具体如下:

信号波动:数值选取或连线不合理所致,建议核实调整后再尝试正确连线。

能耗偏高:可能因型号选择不适当或者配置策略不当所致,建议进行适当的功率选型以及配置修订。

传递误差:有鉴于严重的干扰和不适当的电线排布,我们需要重整电线布局,并增设抗干扰设备以解决此问题。

针对特定问题,在实际操作时需针对性地进行深入剖析和行动调整。

总结

经过严谨的研究分析,我们明确指出DDR上拉电阻在数字系统设计中的重要性。对于其选用、配置及应用,能够显著提升系统稳定性与抗干扰性,并降低能耗。然而在实践操作中,亦需关注布局与连接方式等关键细节,并积极解决常见问题。