DDR3 IP核介绍

多样性动态存储器三代(DDR3)的知识产权核心物件(IP核),被广泛运用于数字电子领域。这款专为DDR3存储器控制功能研发的IP核,能够无缝地整合至现场可编程逻辑门阵列(FPGA)或专用集成电路(ASIC)的设计中。基于其卓越的性能、节能和高可靠性的存储方案,该IP核大大简化了各种数字系统的设计与开发过程。本文将详细阐述其工作机制、特性以及其在实践中的重要价值。

作为资深数字电子工程师,对DDR3 IP核心于现代电子领域发挥的重要作用深有体会。凭借明显提升系统处理速度、有效节电以及高效数据传输功能,该IP核心推动了数字系统科技创新和进步进程。接下来,从多层次剖析该IP核的精髓,深度解析其工作原理并探讨实践应用方式。

DDR3技术背景

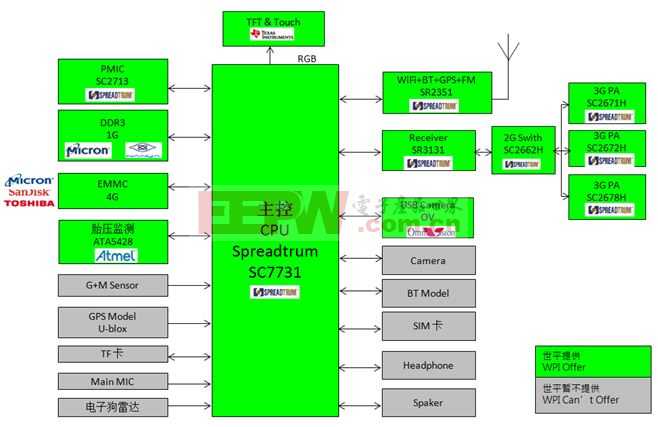

深入了解DDR3技术的本质——它是第三代、双倍数据传输速率的同步动态随机存取存储器(Double Data Rate 3 Synchronous Dynamic Random Access Memory)。与DDR1/2相比,DDR3具有更高的时钟频率、更低的功耗以及更大的带宽优势。其微小且精密的构造包括存储单元、地址线、数据线和时序控制等关键元素。

在信息科技领域中,为了充分利用DDR3存储芯片的快速高效的读写功能,我们采用了高度定制化的IP核设计,实现了合理而有效的存储器控制功能。有鉴于此种需求,选择使用DDR3 IP核便成为了必要的选择。经过精密地调整IP核的各项参数和接口设置,我们得以精确操控 DDR3存储器,享受它所带来的出色的性能表现。

DDR3 IP核原理

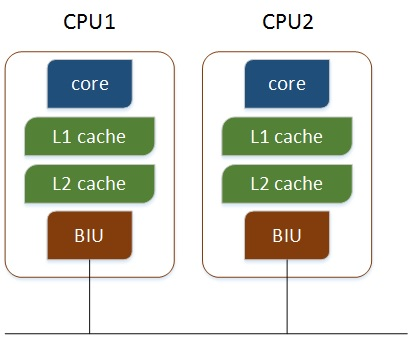

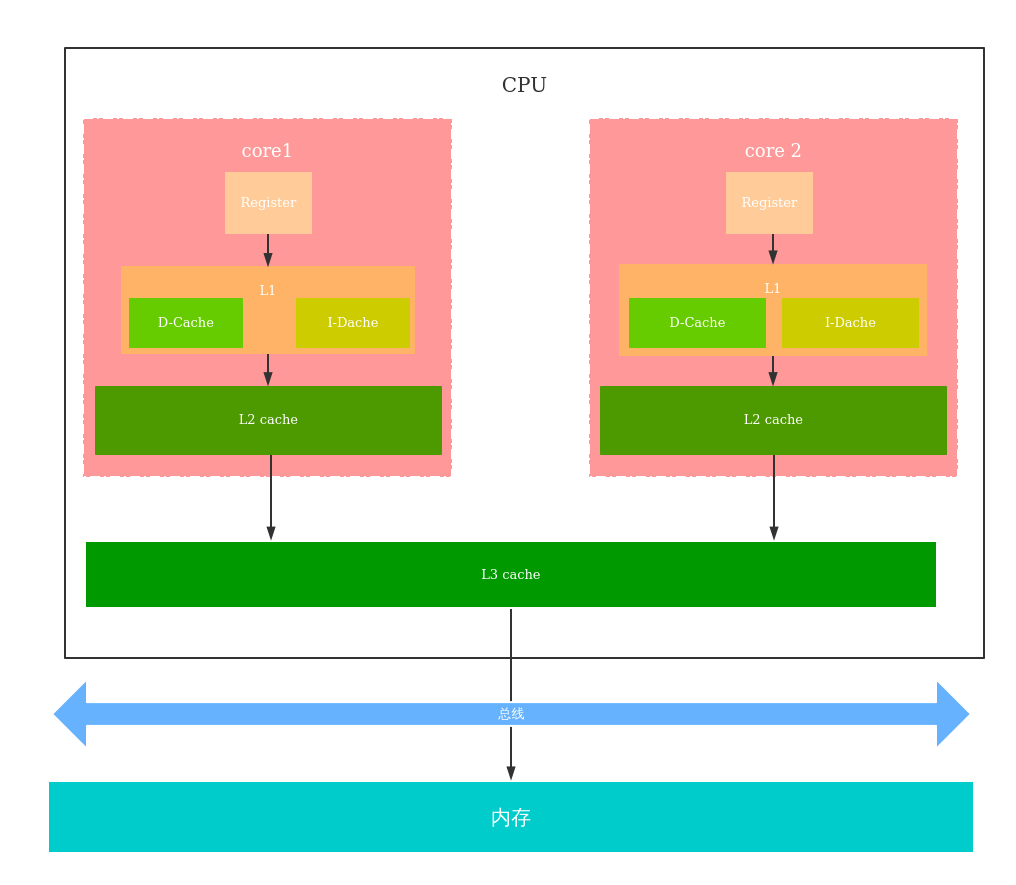

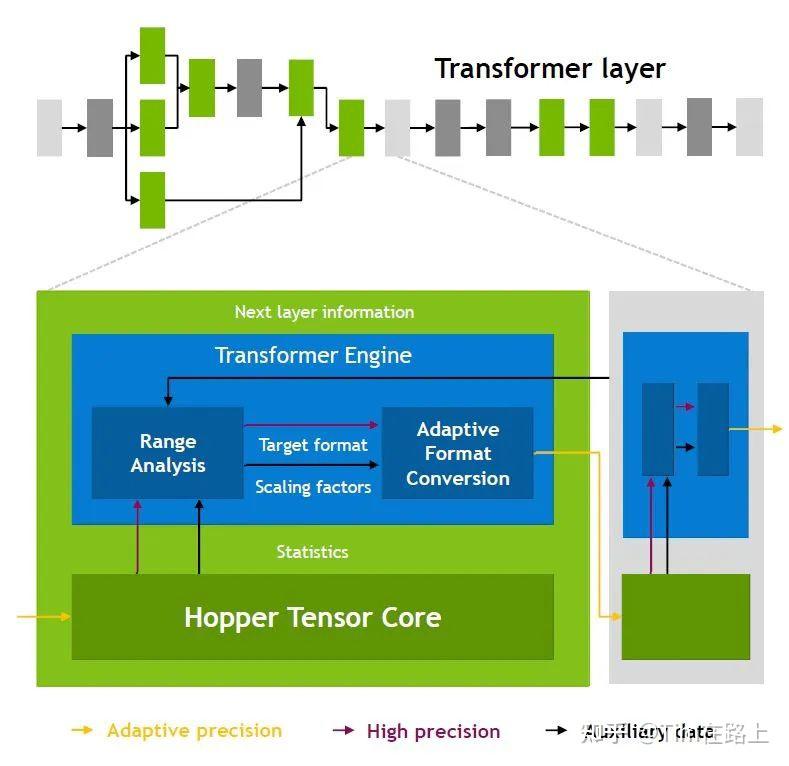

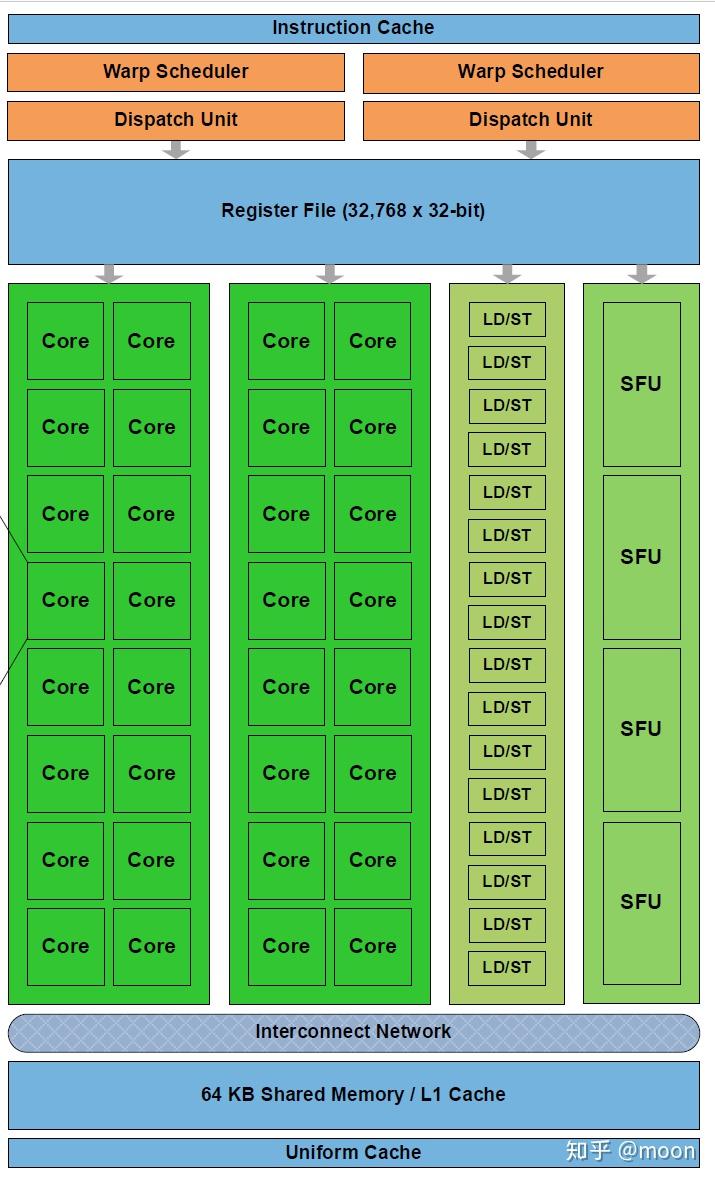

接下来我们将深入剖析DDR3知识产权核(IP Core)的运作机制。其关键结构包括时钟管理单元、数据接口单元、地址映射器及控制逻辑单元等,它们之间协调合作,以保证数据在往复传输过程中的准确有效性。时钟管理单元确保交换数据间的时间同步;数据接口单元负责执行数据的生成和接收操作;地址映射器完成地址空间的转化;而控制逻辑单元则负责统筹各个单元的运作流程。

在实践应用中,DDR3 IP核心采用嵌入式状态机对存储器指令序列及其数据传输流程进行有效管理。借助外部输入信号切换状态,保持与存储器之间稳定且可靠的通信链路。其精心构建的IP核内部逻辑电路和时间顺序控制方案确保了数据传输过程的稳定性和可靠性,从而充分发挥出DDR3存储的全部潜能。

DDR3 IP核特点

详尽阐述DDR3 IP核特性对于更巧妙运用与完善这一先进技术具有指导作用。首先,该IP核具备高度灵活性和可配性,使我们得以依需求调整各项参数设定及接口配置;接着,该内核兼容多种工作模式并提供跨频段数据传输速率调控;最后,其内建自校正功能及误差监测系统,确保高速稳定数据交互过程中的高效安全性保障。

不仅如此,DDR3 IP内核对整体系统节能降耗具有至关重要的影响。通过精心设计其内部电路结构和时序管理措施,可以有效减轻能源消耗压力,实现高性能和环保特性的完美融合,打造出更为节能高效的系统设计方案。

DDR3 IP核在FPGA设计中的应用

fpga设计领域显示出DDR3 IP核的显著价值。硬件的灵活性有效应用于数字电子系统,使其迅速崛起。搭载DDR3 IP核的fpga芯片相较传统芯片,优势尽显,如大幅度提高数据存取的速率和可靠性等。

将DDR3 IP核集成到FPGA架构中的应用,可以显著降低外设操作难度,简化繁杂系统构架,并提升整体系统性能。在实际工程开发过程中,设计师能利用多样化的IP核标准接口,对存储模块进行深入地重新开发和高度适应性调整,满足不同应用场景下关于存储容量及速度的特殊需求。

未来发展趋势与挑战

随着智慧物联网与人工智能新技术的快速发展,对于高效节能和大容量存储解决方案的需求日益增长。因此,DDR3知识产权基础(IP)核在未来数字化电子领域的地位显著提高。为此,该核心需持续改进以适应技术变革的步伐。

在困境中,要依赖创新推动DDR3 IP核的发展。然而,应对市场及技术挑战,如何提高性能、降低能耗,以及增强安全性是我们面临的紧迫问题。只有不断进行创新研究与实践并加以总结优化,才能保证DDR3 IP核技术保持长足的进步。

结语

综上所述,面对当今数字化时代,DDR3 IP核凭借卓越技术优势,已跻身为高端FPGA与ASIC数字系统设计的重要元素。深入解析其工作原理及具体实例,结合各类项目实践,无疑将助力我们更准确地把握这一创新科技工具的巨大潜力及其ur新的拓展机遇。

敬请关注:恳切期望能够听到业界人士关于未来IP Core技术发展的独特见解;以及提升IP Core在数字系统设计中实用效果的思考和建议。期待各路英豪不吝赐教,共同交流分享您的宝贵意见!