什么是DDR3读写时序

DDR3作为主流的动态随机存取存储器(DRAM),其在计算机系统中的关键角色不可或缺。其中,DDR3的读写时序即为数据读取写入过程中各信号间的精确时间配比及顺序。深入理解DDR3读写时序,对于优化内存表现与提升系统稳健性具有重大价值。

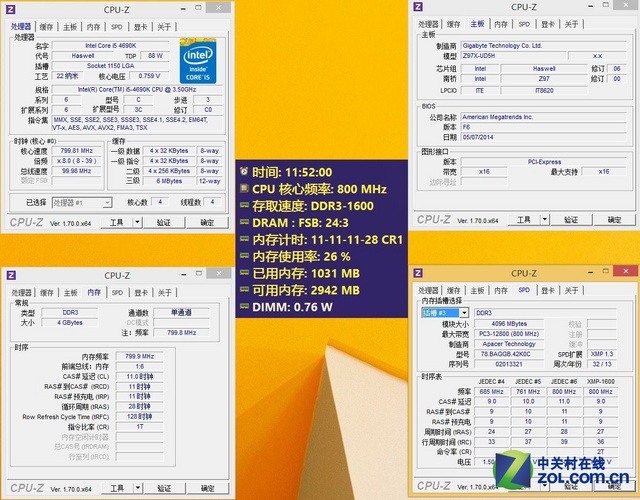

DDR3读/写时序由众多因素共同决定,具体包括CL(CAS Latency)、tRCD、tRP以及tRAS。其中,CL代表列地址选通延迟,亦即列地址选通与数据启动的间隔;tRCD代表行地址选通延迟,反映行地址选通至列地址选通之间的等待过程;tRP则为行预充能延迟,指预充能完毕至下一次行地址选通期间的等候时长;而tRAS则表示行活动周期,即行地址选通后再开展下次预充能所需的最小时长。

影响DDR3读写时序的因素

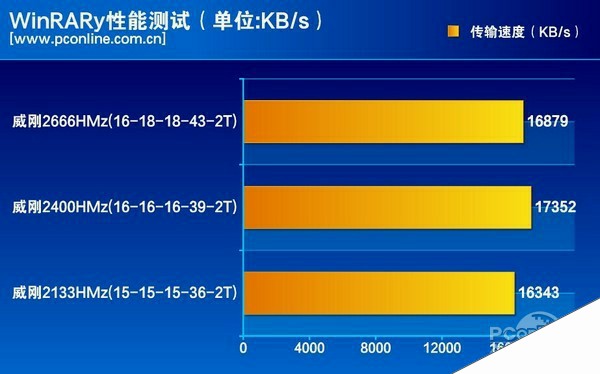

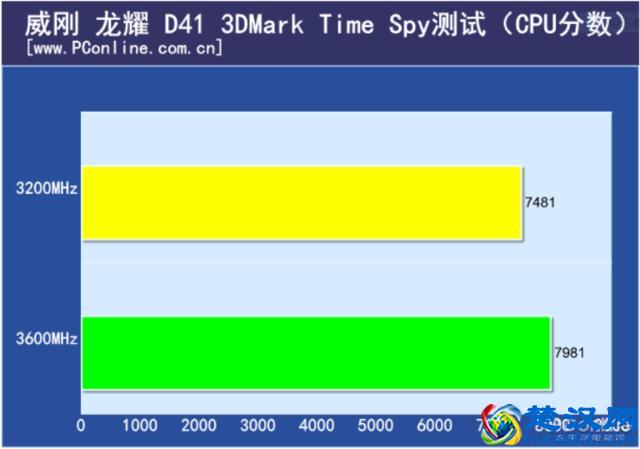

频率:高效内存的频率提升,使其每个时钟周期内达成的任务时间缩减,从而对时序要求更为严谨。

参数:供电电压不稳将使内存在时序操作上出现问题,严重者也可致其损坏。

温度:过高或者过低的温度会对存储器内芯片的信号传输速率产生影响,进一步影响读取写入的顺序。

品质问题:DDR3各类品牌及型号间,由于其存储模块自身质量差异,使得其读取与写入的时间顺序产生差异。

主板设计:各家主板对于内存控制器的设计差异,进而影响到DDR3读写时序。

DDR3读写时序参数详解

CL参数:该数值会影响内存的响应速率,数值越小,响应速度越快,但功耗及稳定性要求随之提升。

tRCD:此参数用以衡量从行地址选择至列地址选择这一过程所需的延迟时间,数值越低,则存储器访问速率相应提升。

tRP:简言之, tRP即是预充结点至下一临界寻址间的最小时延。数值越低,说明内存刷新的速率越高。

tRAS:通过比较不同系统中tRAS的最小值,我们可以发现其数值对内存访问速度的影响,即数值较小的意味着内存加载更加迅速高效。

如何优化DDR3读写时序

1.合理选择内存频率和主板支持频率匹配。

2.调整内存电压以保证稳定供电。

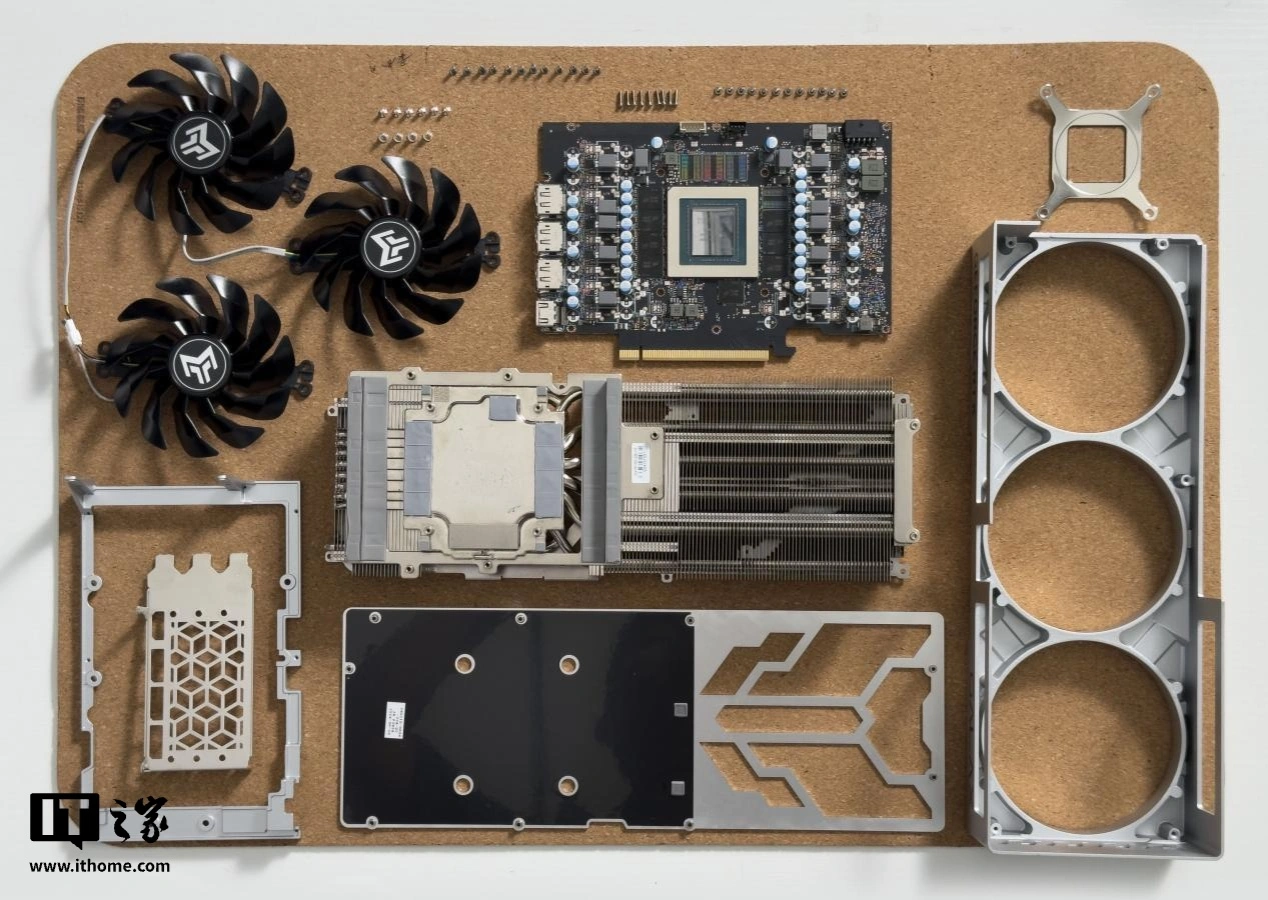

3.保持良好散热环境以维持适宜温度。

4.选择质量可靠、品牌有保障的DDR3内存条。

依照主板规格调整BIOS设定,以便有效提升DDR3的读取与写入性能。

DDR3与其他版本DRAM对比

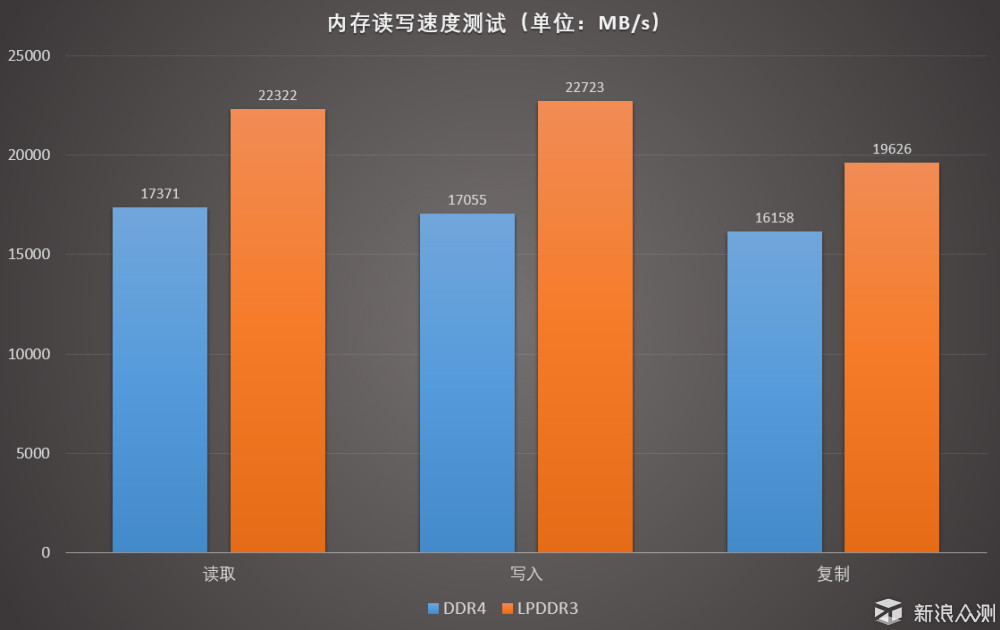

与DDR2及DDR4相比,DDR3展现了其独特的优势,主要体现在功耗、性能以及成本三个方面。相较于DDR2,DDR3的频率显著提高,同时功耗亦明显下降;然而,与DDR4相比,尽管DDR3在频率及功耗方面稍显落后,但在价格方面却具有很大竞争性。正是基于此,即便在当下的中低端计算机系统中,仍广泛使用DDR3作为主内存。

未来发展趋势

伴随科技飞速进步,DRAM领域亦不断推陈出新。未来,如DDR5与LPDDR5等新世代内存技术日渐流行,DDR3终将淡出视野。新的内存技术更强调在功耗、带宽以及容量三方面取得平衡,从而提升计算机系统的整体性能水平。

结语

透彻剖析DDR3读写顺序,方能充分认识到此重要因素对计算机系统效用的驱动作用。适当调整和优化DDR3顺序可显著提高系统运行速率,加强系统稳定性并延长使用寿命。伴随技术革新的步伐,新一代内存技术给人们带来了无尽期许。您对未来内存发展趋势又有何高见?如何评价目前仍在计算机系统领域发挥重要作用的DDR3?