身为电子工程师,本人深谙DDR3布线之道。现代电子设备常采用DDR3内存作为存储器件,其运行效能与稳定与否直接影响整体系统表现。因此,恰当的布线设计便成为DDR3内存正常运作的核心因素之一。本篇文章将重点探讨DDR3布线需求的基础概念、布线指南、信号完整性、时序匹配、终端匹配及层间叠加等方面,旨在为广大电子工程师提供具有实际操作性的参考建议。

1. DDR3布线要求概述

DDR3内存,高性能同步动态随机存储器(SDRAM)的代表,工作频段介于800MHz至2133MHz之间。为保障其正常运作,应严格遵循特定的布线规矩。这些要求涵盖了信号完整性、时序匹配及终端匹配等关键领域。在这之中,信号完整性的掌握尤为重要,对信号质量与稳定度起着决定作用。

DDR3布线务必时刻关注信号传输过程中诸如线路长度、阻抗匹配程度、交叉情况以及多层堆栈等一系列影响因素。适当规划DDR3布线能显著降低信号干扰与时序误差的发生率,增强整个系统的稳定性及可靠性。

2. DDR3布线原则

进行DDR3数据布线设计需遵循以下基本原则:1.尽量缩短信号线路长度及传递时延,降低延迟;2.保证稳固的地级针脚连接,减小接地区分阻抗,提升信号传输品质。

针对差分信号布线策略,需确保其保持优良的匹配状态,以规避信号失真的风险;并严格管控数据线与地址线、控制线之间的交叠状况,以免产生不必要的干扰事件,保障系统的稳定性。

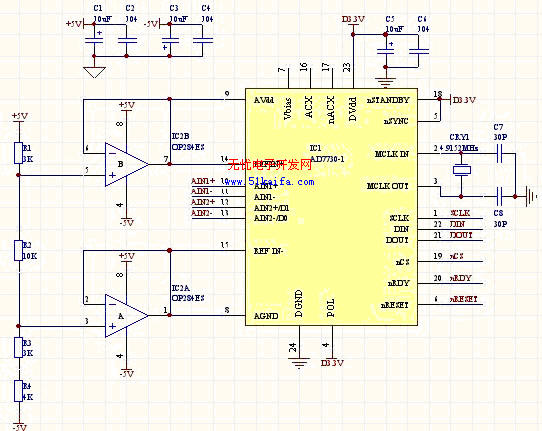

3. DDR3布线中的信号完整性

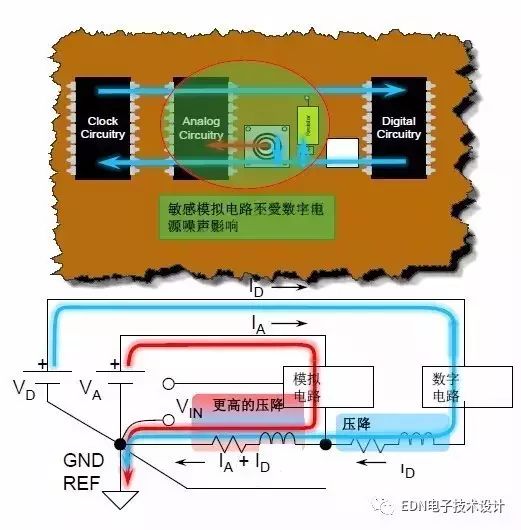

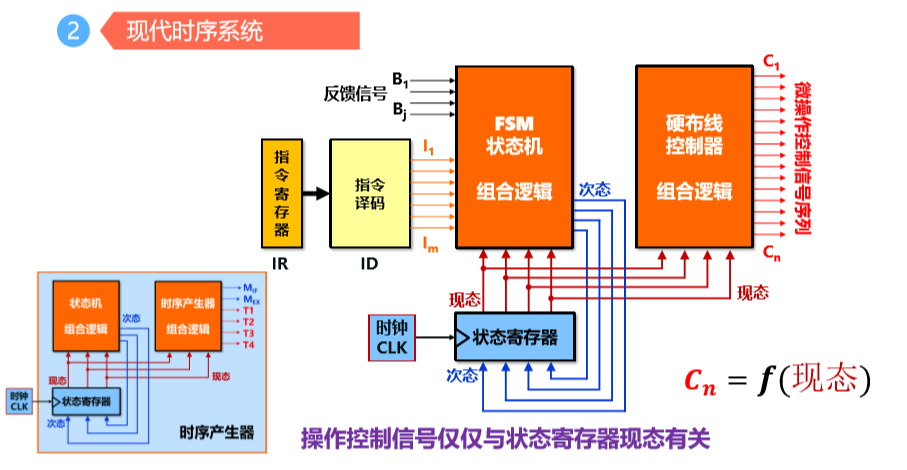

在DDR3布线设计技术领域中,信号的完整性具有举足轻重的地位。其重点在于操控各种时序参数以及亲属数据时序和时钟分配,如此便可有效抑制信号传输中所遇见的串扰与反射现象。

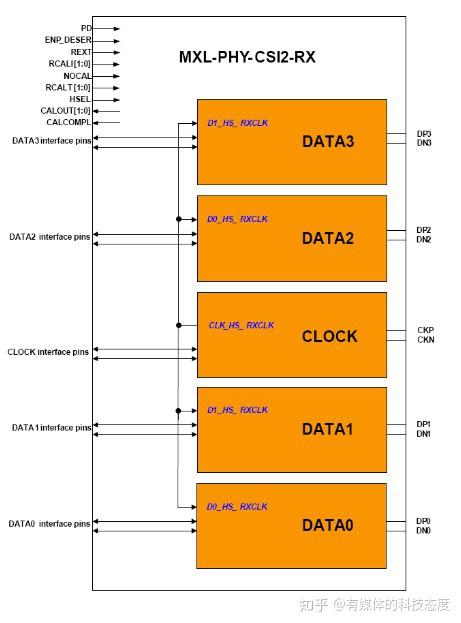

为了确保DDR3内存的时序得到精准掌控,在布设控制信号线路时务必重视各类信号的协调搭配,同时还需充分符合正确的时序需求。另一方面,对数据时序而言,在搭建数据传输通道之际,应充分思考数据抵达目标设备所需的时间和可能存在的时间延迟。

另需注意,时钟配置中,应确保在各数据线路上共享时钟源来驱使所有设备,并确保每个设备接收到同步精准的时钟波形。

4. DDR3布线中的时序匹配

DDR3内存体系中,各组件时序紧密相连。在模块布局与连线设计环节,必须严守时序匹配原则,以防止资料误输或系统瘫痪。

为确保时序一致性,设计阶段必须保证各模块间数据传输路径的长度均等或经过相应调节以达到最佳延时效果。同时,也应关注不同模块间的触发次序和数据到达时间因素。

适当的路线和延时设置,能使各零部件间连接稳定,保证系统运作无误。

5. DDR3布线中的终端匹配

终端适配即通过自身与对方的阻抗适配,在差分信号传输中降低反射与串扰影响,此原则亦适应于DDR3存储体系。

终端阻抗值需先确立,再配以相应终端电阻以达至阻抗匹配。此外,尚须关注终端驱动力及遥感电阻与拓扑结构间的相互影响。

通过精确设定终端阻抗及合理安放终端电阻,能显著提高差分信号的传输品质,同时降低系统中的噪声干扰。

6. DDR3布线中的层间叠加

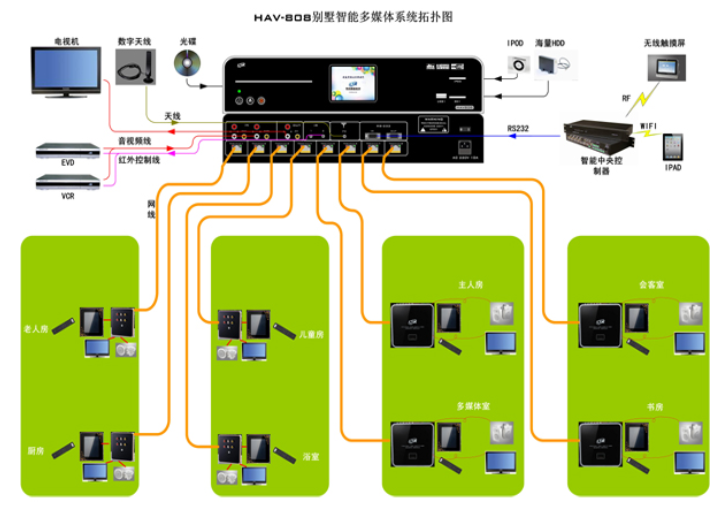

多层次PCB板即把多种性能或型态的讯号层层重迭,进而创建多元PCB板。此种技术在DDR3内存模组设计中被采纳于更高效地满足复杂电路连结所需,进而增强系统稳固性及耐久度。

合理安排各功能层次空间配置,深度厚度适宜可以降低信号串扰及其影响,同时提升整个系统的抗干扰性能。

进阶设计中需重点关注板厚设定、板材料选定及各层电气连通方式等环节,确保整套设备具备优良的电气属性和稳定性能。

7.总结与展望

经过深入探讨与分析DDR3布线设计的关键要素,我们认识到,正确、高效地开展DDR3内存模块的线路规划,对系统的稳定及可靠运行起着决定性作用。要实现这一目标,我们务必要详尽理解并严格遵守DDR3内存模块的布线原则,同时根据具体情境运用各类科技措施,实践过程中不忘反思,汲取教训,持续完善与优化。唯有如此,方能满足如今复杂电子产品对高速且稳定的DDR3内存模块日益增长的需求。

在科技创新及其市场需求变动的推动下,DDR4及LPDDR4等新型内存在未来将逐步取代DDR3,位居市场主流;同时,相关技术准则亦会同步革新。为此,我们需要紧跟时代步伐,持续调整和完善知识储备,以适应新技术和新规范带来的挑战,力争实现个人专业素质及成就的更大突破。