现代电子设备,涉及DDR3内存这一关键组件,其性能直接影响体系的运作速率与稳定性。为了保证内存模块的正常运转,布线的规范性、信号传输的完整性以及时间先后顺序都必须严格遵循。本篇文章将针对这些要点做深度解读。

一、DDR3布线规范

DDR3存储器的布线规范对于保障其与主板间信号的稳定传输至关重要。在电路板的设计过程中应严格遵循JEDEC颁布的各项相应标准(如JESD79-3E及JESD209-2B)。该类规范规定了各类信号线路的布局、长度及阻抗等方面的需求,进而确保信息传输的精确性与可靠性。

实际布线过程需重点关注差分对、匹配延迟及信号层隔绝原则。差分对走线应保证长度一致,避免相位失衡;匹配延迟则需准确控制以防时序错误,对于多层板设计来说,信号层间还需拥有充足地层隔离以减轻相互影响。

二、DDR3信号完整性

DDR3内存于高性能条件下运行时,信号完整性至关重要。其主要涉及到的因素包括传输线路阻抗匹配、反射及串扰控制等。在布线设计过程中,应依据PCB材料特征与制作规定确认适宜的阻抗数值,同时运用仿真工具加以核实。

在DDR3内存控制器与PHY芯片连接时,必须注重驱动力度与接收敏感性等关键参数。需精心设定驱动器和接收器以提升信号质量及减少能耗。此外,高速条件下应采纳双向差分对布线方式,同时严格控制串扰来源,降低其对信号质量的干扰。

三、DDR3时序要求

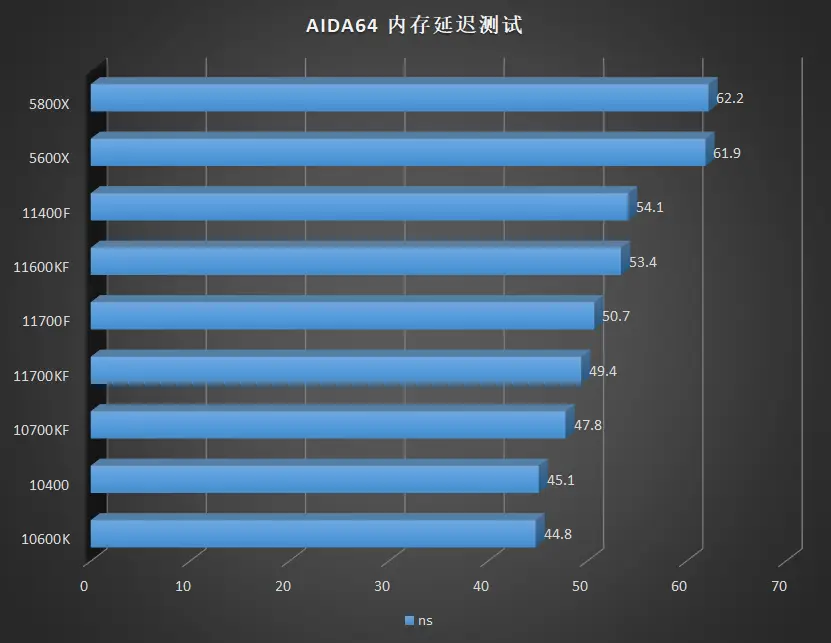

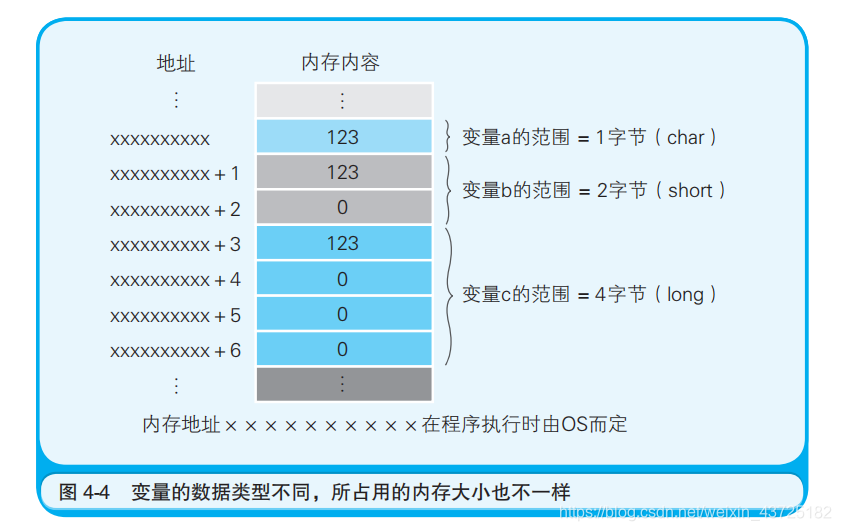

DDR3内存要求极高精准度的时序规范,这对于实际系统设计至关重要。对其的涵盖主要集中于几个重要方面:预充电时间、写入延迟以及读取延迟。预充电时间是指在执行读写操作用前,需要为内存预留充分的准备时间;写入延迟与读取延迟则分别代表着指令发送至实际数据传输起始间的过渡期。

为确保时序要求,PCB设计需关注走线长、延时配以及终端阻等要素。此外,需量化温变与电源波对时序参数之影响,并在实际测试中进行严谨验证。唯有严守时序规定,DDR3内存方能正常运作,发挥其最佳性能。

四、DDR3布局原则

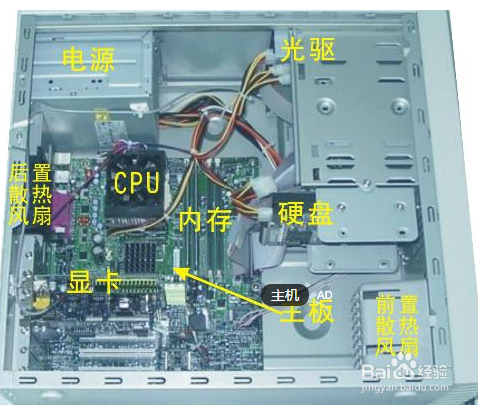

布线技术和信号完整性的实现对DDR3内存极为关键。此外,合适的组件布置与电源与散热设计对于保证系统稳定可靠至关重要。布局设计还需注意,尽量缩短数据通道距离,从而规避可能的干扰。

在多元内陆存储系统中,不同通道间需保持等长和定向,同时避免公共数据/地址线路引发的冲突,以此实现高效系统性能提升与降低隐患风险。

五、DDR3布线优化技巧

为提升DDR3内存系统性能及稳定性,以下有若干精细优化策略可采用:通过飞线连接法缩短数据传输路径;运用仿真软件对各应用环境做出深度剖析与评估;精选PCB材质适应高速运行要求。

实践过程中,基于接触面扩大或增加焊点数量,可提升线路连接质量;借鉴盲埋孔工艺技术增厚电路板,增强阻抗控制力,从而优化DDR3内存系统布线布局。

六、DDR3故障排查与修复

即便经过精心规划与精密调校,DDR3内存模块也难免偶尔出现故障。需运用专门设备进行检测并根据实际状况进行维修工作,常见故障有时序违规、信号扭曲以及电气线路故障等。

面对各类故障,可采用逐层排查技术定位问题,通过替换零件或调整参数加以修复。此外,运用逻辑分析仪及示波器等专业仪器进行辅助监测与医治,确保迅速维修,使系统重回正轨。

七、未来发展趋势

伴随着科技的持续进步,DDR4内存已逐步取缔DDR3,引领新一代市场主流产品潮流。同时,DDR5乃至DDR6内存尚在开发阶段,预计将带来更高速度及更低能耗优势。因此,对于未来DDR内存系统设计,我们应着手实现高速传输技木与低效能优化的无缝衔接,紧随新技术变革之路。

综观而言,DDR3的布局需求涵盖了规范遵循、信号稳定性和时序参数等诸多要点,而实际设计过程中需综合权衡考虑,以实现系统稳定运行。