DDR4布线规则的重要性

DDR4以主流存储规范身份,其布线规范对于系统稳健性与性能提升具有关键影响力。若能恰当运用DDR4布线原则,不仅可有效降低信号干扰,加速内存传输效率,确保系统数据稳定可靠以及保持相互间冲突的致性统一性。故此,理解并遵从DDR4布线规范乃是设计高效计算机系统过程中的必要环节。

对于实施 DDR4 内存模块线路布置,务必要虑及诸多复杂因素,如信号完整性、传输延迟以及电磁兼容性等,从而确保数据能够迅速且稳健地从内存芯片传递至处理器中。因此,采用科学、有效的布线规范至关重要,以尽量减少信号失真以及串扰等故障现象发生。

内层布线和外层布线

在设计DDR4内存模块布线过程中,需关注内、外两层布线。其中,内层布线路径于PCB板内,用于连接芯片间信号传输,对速度及稳定起决定作用;而外层布线链接了内存接口及控制器,对系统整体表现产生重大影响。

在内层布线过程中需注重差分对长度匹配、走线宽度与间距对信号延迟及功耗损耗的影响;在外围布局方面,得关注信号环路、阻抗匹配以及电磁兼容性等要点,确保持续、优质的数据传输效果。

差分对长度匹配

差异化对长距离匹配乃DDR4线路布局之关键理念。鉴于DDR4运用了差分信号传递术,即将互为反相且振幅等同的正负两信号共同传送,以便降低串扰,提升抵抗干扰能力。故而在设计DDR4记忆体模组时,务必确保各对差分信号间的长度尽量保持均衡,以避信号失真与时序偏差。

实践应用中,通过科学规划PCB板布线,运用诸如交错排列的独特布线条路技术,得以实现差分对距离参数的精确配合。这不仅大大提升了系统抗干扰性,还有效减小串扰效应,确保了数据传输速度及稳定性。

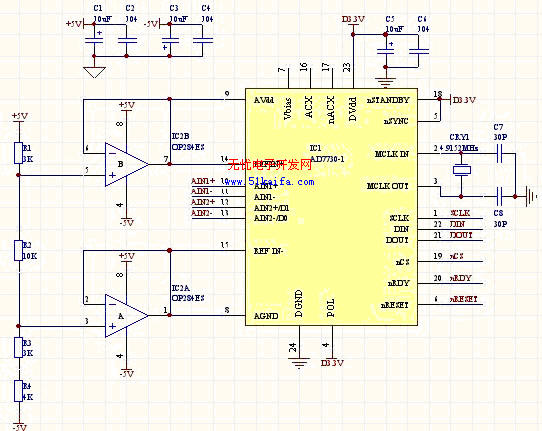

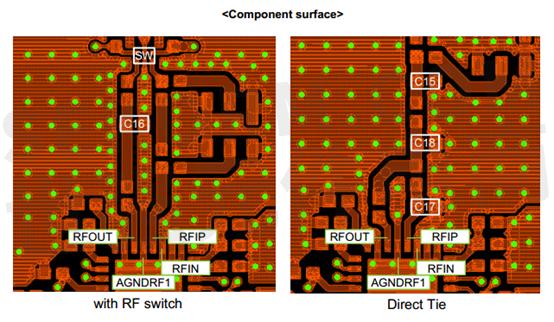

阻抗匹配与电磁兼容

除了精确差分对长度设计,阻抗匹配和电磁兼容性在DDR4的布线过程中亦属关键考虑因素。所谓阻抗匹配主要任务在于使信号源(如控制器)的输出端阻抗与传输媒介(例如PCB板)载波端口的阻抗达到兼容状态,以此减低反射损耗,提高信号质量。

在设计DDR4内存模组时,应针对特定条件选取适宜的阻抗值,并借由调整布线宽度及距离等参量,让其达到最优的阻抗匹配效果。同时,当涉及到电磁兼容问题时,应当重视减小组合面和降低辐射干扰等环节,确保整个系统稳健运作。

时序校正与调试

在成功设计DDR4内存模块之后,接下来是至关重要的时序校正和调试环节。其中,时序校正如使用专业仪器对其各信号点传输时长执行精确的测量,再参照特定时序规范进行微调,从而保证数据在准确的时间抵达指定设备。至于调试部分,中包含了逐步检验所有信号通道运行状况、找出异常波形等关键步骤。

通过严谨的时序校正和调试程序,可有效识别及修复潜在问题,以保障系统稳健运行,且能达成预期性能目标。

技术发展趋势

随着高新科技的持续发展与市场需求的增加,DDR4布线规范的新技术与变革表明在这一领域的变化正在发生。譬如,未来DDR5标准有望展现出更高的工作频率及降低电力消耗的优势,对于差分对的长度以及阻抗匹配度亦将设定更为严格的要求。此外,PCB设计工具则会趋向于更加智能化和自动化以帮助设计师解决更为复杂的DDR4布线问题。

深刻理解并遵守DDR4布线规定,对于优秀计算机系统的设计而言至关重要。唯有精准规划与严谨实施相关标准,方能在保证数据传输速度及稳定性基础上实现整体效能的提升。