什么是FPGA DDR3控制器

FPGA(现场可编程门阵列)作为高灵活性与高性能优势兼具的可编程逻辑设备,其核心要素之一就是DDR3(双倍速率3)内存控制模组。这一控件不仅充分发挥了FPGA的潜能,更保证了DDR3内存的高效运作,对FPGA系统整体表现产生决定性的影响。

在现代化计算系统环境下,内存子系统的效能及其稳定运行对于系统整体运作速率及效益具备关键影响。对此,FPGA DDR3控制器作为连接FPGA及DDR3内存间的枢纽,担当着重要的角色;透过深挖并改良FPGA DDR3控制器,有助于提升系统总体性能,更可加速数据传输,增强系统响应能力。

FPGA DDR3控制器的工作原理

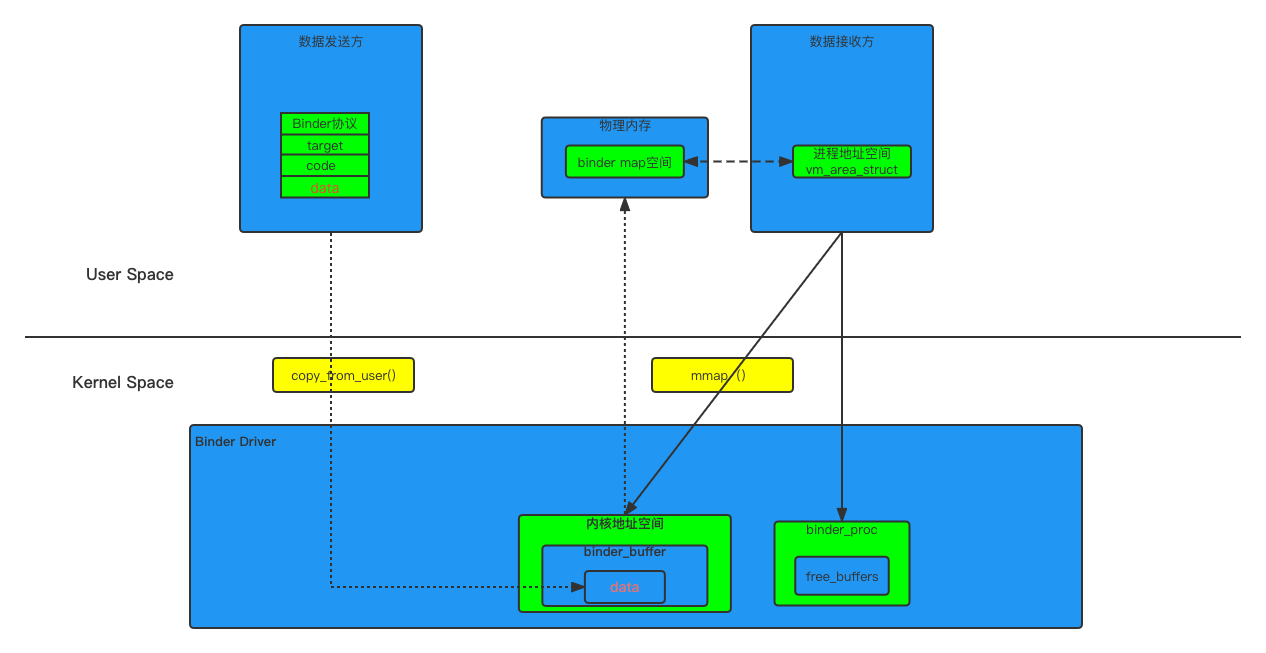

FPGA DDR3控制器主要实现FPGA与DDR3存储器间数据交互以及信息交换的有效协调。其核心流程可以简要归纳如下:

初始化阶段: FPGA DDR3控制器需在上电或重启后,对时序参数和地址映射等关键参数进行详细的配置。

写操作流程:CPU或外设向DDR3内存进行数据录入时,会首先将该指令传达至FPGA DDR3控制器。控制器依据特定请求生成指令序列,随后执行到DDR3内存储器的数据写入操作。

读操作:若CPU或其它设备需从DDR3内存索取数据,请求会传输至FPGA DDR3控制器。该控制器据此发出适宜指令以获取数据,并传送回CPU或设备。

数据校核:在资料存写或读取过程结束之时,FPGA DDR3控制器会进行严谨的数据检验程序以维护数据传输的精确性与全程无误。

FPGA DDR3控制器的设计与优化

成功设计稳定且有效能的FPGA DDR3控制器需兼顾并协同优化以下多个方面:

时序布局:调整适当的时钟频率与顺序参数,确保数据运送的稳定性与安全性。

优化数据通道设计:运用高效的数据路径构架,有效降低延时、提升处理效率。

3.控制逻辑设计:优化控制逻辑,减少冲突、提高响应速度。

状态机架构:精心设计对应不同场景的态设,高效有序地完成数据传递任务。

差错处置规划:配备严密的诊断及修复体系,大幅提升体系抵抗事故的能力。

如何优化FPGA DDR3控制器性能

为了提升FPGA DDR3控制器的效能,可行措施有如下几类:

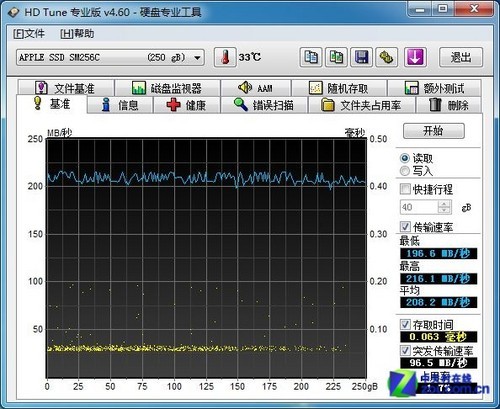

时序优化:精心调整时钟频率及时序参数,全面提高系统稳定性与运行效率。

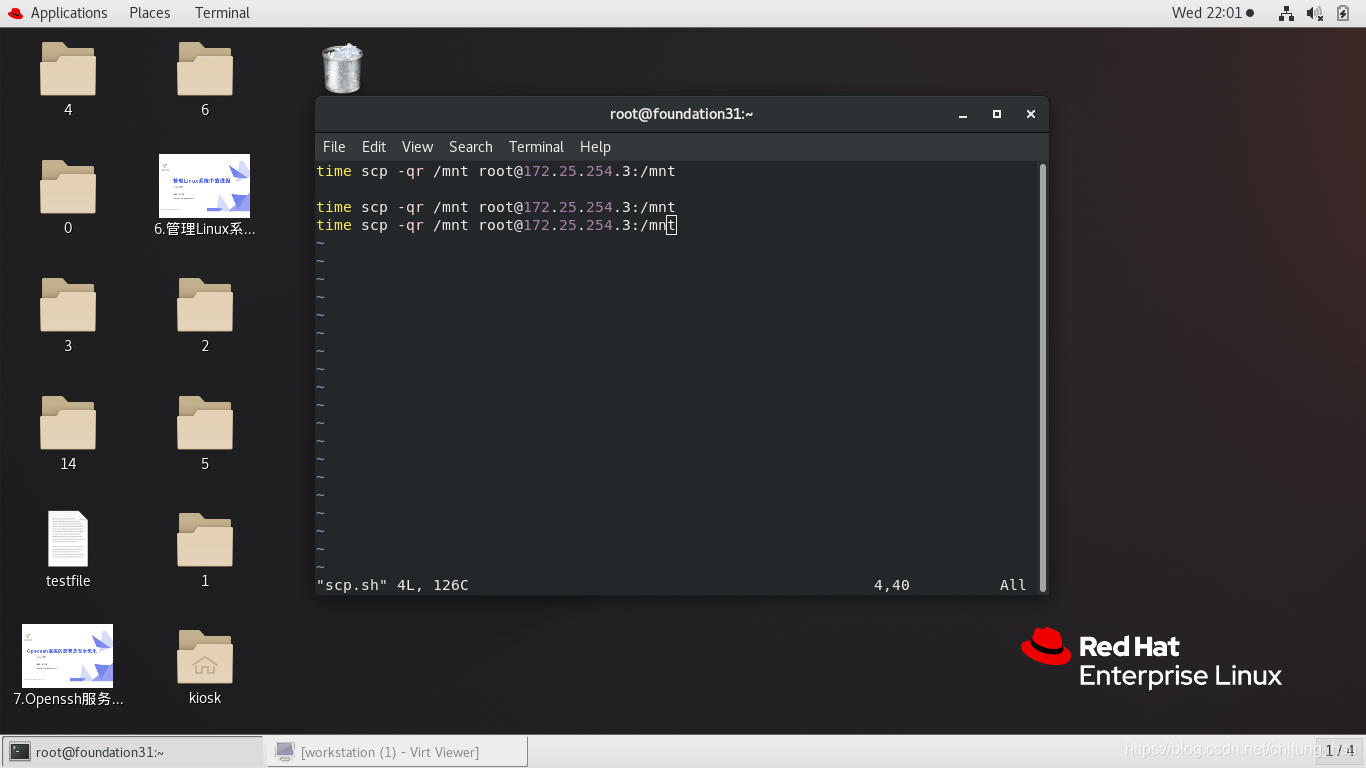

并行传送提升:合理运用并行传送手段,确保稳定性基础上有效加快信息传播速度。

精细化数据缓存配置:设定适宜容量与高效性能,降低频繁访问DDR3内存在所引起的延迟。

异步传输优化:通过实行异步传输策略,可更有效使用系统资源并降低能耗。

5.算法优化:通过改进算法实现更有效率地数据处理和传输。

FPGA DDR3控制器应用领域

FPGA DDR3控制器广泛应用于各种领域,包括但不限于:

通信行业:FPGA DDR3控制芯片用于基站及光纤通信设备中的高速数值处理与信息交换。

图像处理方面:利用FPGA DDR3控制单元,可高效执行医疗影像及工业检测涉及的图像获取和处理操作。

高性能计算领域:在大型计算机系统及云端服务器工作环境中,利用FPGA DDR3接口控制器实现计算性能的增强。

汽车电子应用领域,通过采用FPGA DDR3控制器于汽车电子系统内,提供完善的车载信息娱乐与驾驶辅助服务。

未来发展趋势与挑战

随着科技进步加速,人类对计算速率与处理性能的要求也在日益提高。预计未来FPGA DDR3控制器将呈现出以下种种发展趋向及挑战。

高宽带需求:随着大数据、AI等技术的广泛运用,对高带宽内存访问的需求愈发强烈。

极低功耗需求:随着移动电子设备、IoT等行业的迅猛发展,人们对于高效节能产品的需求日益迫切。