身为电子工程师,对DDR3的时序解析深有体会。DDR3作为主流动态随机存取存储器(DRAM),在现代化计算机体系中居关键地位。透彻研究它的时序解析,能深化我们对运行机制的认知,为系统设计及优化提供极其宝贵的参照。以下,从时序观念、时序指数,以及时序关联诸方面进行深度剖析。

1.时序概念

在开展DDR3时序研究之前,务必领会几个关键的时序理论.时序即数字电路中的信号流动节奏,对信号稳定度与准确性具有直接影响。作为DDR3电子元件之一,其内部的多元复杂时钟及数据信号在数据交互中需严格把控各信号的抵达时刻,以保证数据能够的准确传输。典型的时序包括写操作时序、读操作时序以及预充能时序等方面。

对于DDR3而言,时序分析包括四大方面:写入操作、读出操作、预充电路操作及自我刷新操作。各个环节均遵守严格的时间设定与程序规制,只有遵循所有规定和要求,方能保证DDR3设备平稳运行。

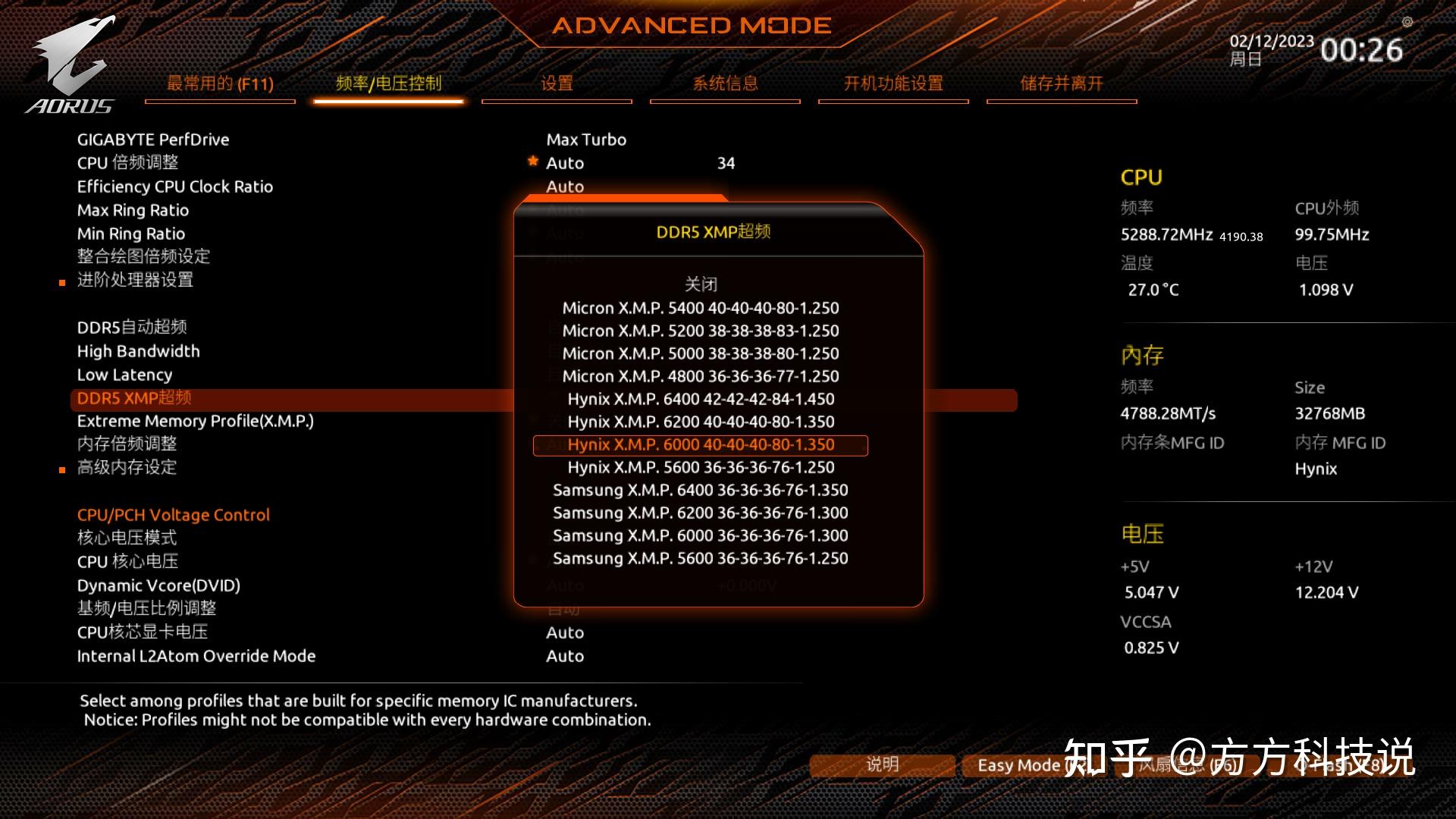

此外,实施DDR3时序分析需充分意识到各品牌内存芯片间细微差异的存在,需要针对特定规格的芯片进行相应的参数配置及调整。

2.时序参数

DDR3时序分析中,关键要素须引起重视,如:

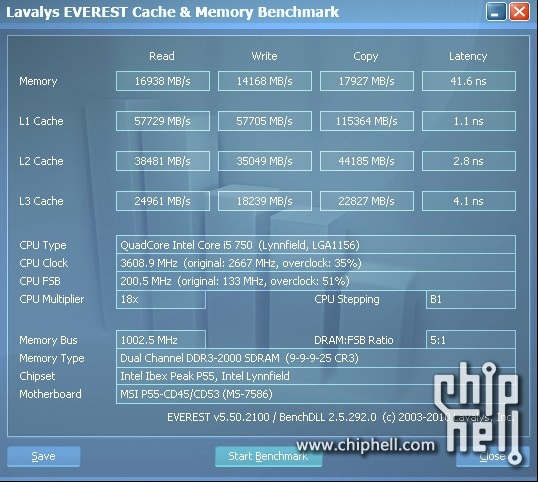

- CL:即CASLatency,显示了列寻址开始至数据读取/写入操作获取有效数据的时间跨度。

tRCD (RAS to CAS Delay)是指行址转至列址所需的时延,此参数象征了从行址启动有效到列址发动有效间的等待时间。

- tRP(Row Precharge Time):指代行预充电所需时间,代表访问相邻不同行之间所需等待时长。

- tWR(Written Recover Time):写入修复时段,在发出写入指令之后需待时多久方能实施后续指令操作。

- tRFC(Refresh Cycle Time):代表刷新周期的最短时间间隔,是两次自动刷新的必要间隔。

此等精密参数直接决定了DDR3内数个信号的同步与稳态表现。精准设定及适时微调,可优化DDR3内存模块的整体性能。

3.时序关系

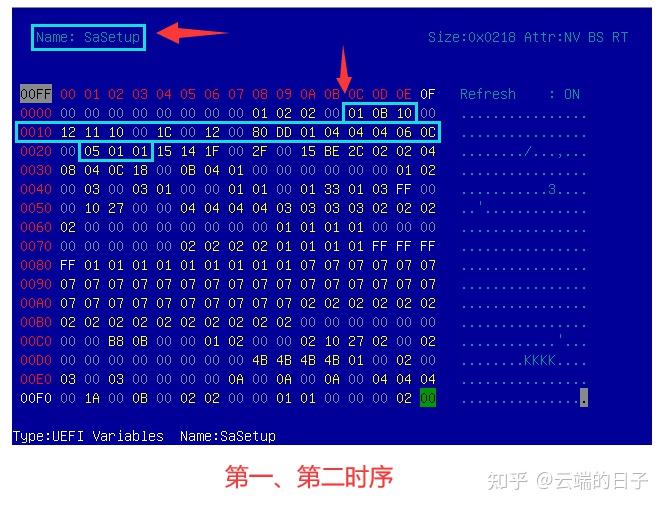

对于DDR3时序规律的深度剖析,必须深化对各异信号间互相影响之理解。例如在将原始数据传输至DDR3内存模组的过程中,需依序遵循如下流程:

-发出写入命令;

-等待CL设定的时间后发出列地址;

-等待tRCD设定的时间后发出列地址;

-等待tWR设定的时间后发出下一个写入命令。

步骤之间要求严格的顺序和时间规定,设计环节必须精准把控各步骤所需的进度,以确保信号之间的和谐一致性。

同样复杂的关系还表现在数据读取过程中,以及预充能与自动刷新过程中的时序需求。因此,要保证DDR3内存模组的有效运转,就必须对上述时序状况有深入认识并进行适宜的系统结构及参数配置规划。

4.仿真与验证

为确保DDR3内存模块的设计能满足时序标准,采用仿真工具对其做出验证是必要且有效的流程。通过创建适当的模型和严格设定的测试用例,再结合精准的参数设定,我们就能够全方位地审视该设计方案在遵循DDR3规范所订立的所有时序指标上所具有的表现力。

验证与测试乃确保系统稳定性及可靠性之关键方法,应于设计阶段发掘隐性问题并及时处理。经对设计方案持续优化,结合实际仿真数据调整,可提升系统设计品质,达致更优性能效果。

5. DDR4与未来发展

随着科技的飞速发展,DDR4已替代DDR3崭露头角,引领新一代主流内存规格。相较DDR3,其频宽、能耗及存储器容量均有显著提升。然而,在设计和使用DDR4之际,时序分析及优化工作依旧至关重要。

鉴于计算范畴的不断扩展以及升级所带来的需求,内存技术正在经历演变和改善。诸如NVDIMM、HBM等创新型存贮设备已逐渐进入市场并获得了广泛应用。面对这一瞬息万变的市场格局及激烈的竞争压力,深入了解内存技术的发展动态以及专注于此领域显得至关重要。

6.结合实际案例

实际项目中的问题解决经验,不仅对于理论理解具有支持意义,更是深入领悟项目本质的必要途径。分享成功案例可助人更有效进步与成长。

譬如,在一个项目实施过程中,屡次遭遇因误设tRCD参数而引发的内存读错和系统稳定性问题。严谨排查及剖析后确认了症结所在,然后通过调校该参数并进行严格的测试验证,成功根除了这个问题,并且有效地维护了系统的日常运作。

7.总结与展望

总结而言,DDR3时序分析堪称复杂且颇具挑战性之领域。唯有深刻洞察其原理,熟知重要参数,精细化设计方案并结合丰富实践经验多方考虑,方能出色履行相关职责。

随着科枝的飞速推进和发展,内存技术必将实现新的革命和突破。我们必须紧跟时代步伐,追求不懈地钻研创新,将理论知识付诸实践以促进行业发展。

期望此文能为各位读者在研究DDR3时序分析方面提供宝贵启示和专业支持;诚邀各位读者踊跃参与讨论和分享,共同推动行业发展。