什么是DDR4 DQS

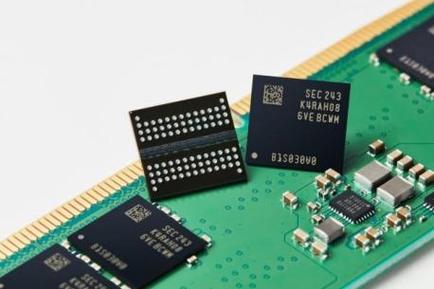

DDRTM(四代动态随机存取存储器)中的DQS,为Data Strobe (DQ/DQS)信号,是内存结构中不可或缺的元素。在DDRTM中,DQ代表数据传输通道,而DQS则负责同步数据通道上的时序,是保证读写操作稳定可靠的重要信号。通过精准控制DQS信号,实现了对内存事务处理的严格把控。

DDR4内存内的DQS信号生成与传输机制严谨且精细。内存芯片利用自身时序控制逻辑来产生DQS信号,之后将其输送给主板控制器。控制器识别并分析了来自DQS信号的时序信息后,调理数据线的数据,实现内存内存读/写功能。

DDR4 DQS的作用

内存中的存取顺序受控于DQS信号。在读取环节,主板控制器需依据该信号选取数据线的数值,并将之转译成相应的数字信息;反之,在写入动作中,DQS信号亦决定了何时向数据线上传输相关数据,从而决定了内存存取过程的精确度及稳定性。

在DDR4内存设计与运用过程中,由于其高频且大带宽的特性,使得对DQS信号稳定性的要求更为严格。任何对该信号的干扰或迟延问题,均极有可能导致内存运转失效乃至产生错误,进而严重损害系统性能以及稳定性。因此,为保证系统运行的稳定性和可靠性,我们必须高度关注并合理地规划与调整DQS信号布线。

DDR4 DQS的优化

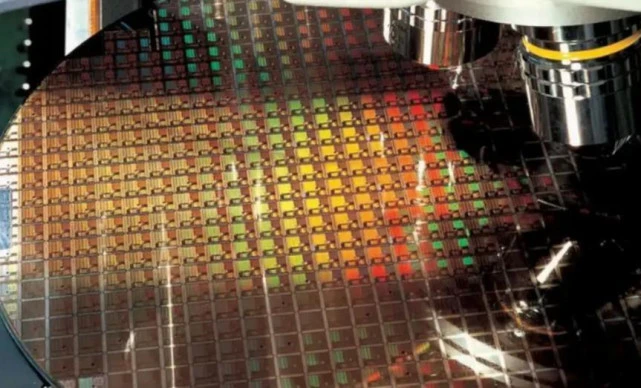

关于DDR4 DQS信号的定制化改良,实际运用中需特别关注时序设计和电磁兼容两个关键领域。时序设计环节必须依照规范严格调整DQS信号的延迟和相位等参数,以保证与数据传输同频且稳定性优越;而在电磁兼容设计上,应极力避免干扰源头对DQS信号传输产生影响与否,诸如尽可能降低高速数字线与DQ/DQS走线之间的平行度等措施坚决实施。

此外,针对DDR4内存控制器,我们还能运用诸多优化策略。如选用优质且拥有更低延迟的晶体振荡器以提供更精确和稳定的频率;对电路结构进行优化,以缩减能耗、增强抗扰性等等。这类手段均能显著提高整体性能,以及在实际操作中满足大容量,高速数据处理的需求。

结语

在DDR4内存模块中,DQS是一种关键的时钟信号,在数据读写过程中起着核心作用。深入理解它的工作原理及其在内存中的角色,并采取相应的优化策略,能够提升系统运行的效率与稳健性,更加高效地进行DDR4内存模块的应用和调试工作。