DDR3内存概述

DDR3内存为市场上常见的动态随机存取设备,广泛运用于各类计算机硬件系统之中。相较于DDR2产品,DDR3内存具备高频、低压及宽频等核心优势。其内部结构主要由若干存储晶片、控制逻辑及线路构成。值得注意的是,DDR3内存中的OTD(On-Die Termination,内置终端电阻器)特性,对于提升总线性能与信号稳定性有着决定性的影响。

DDR3 ODT原理概述

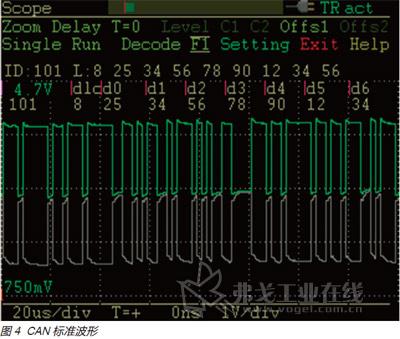

ODT(Optimum Decoupling Terminal)即在DRAM模块内设定的终端阻抗匹配机制,用以匹配传输线路的特性阻抗,从而改善信号匹配及消除反射现象。DDR3内存中,ODT主要由动态与静态两类技术组成。其中,动态ODT随数据传输同步进行终端阻抗调整;静态ODT的终端阻抗在初始阶段即已固定。通过精确设置ODT参数,可大幅降低信号反射及串扰,进一步提升总线传输效率及稳定性。

DDR3 ODT工作原理

在DDR3内存运行过程中,ODT发挥着终端阻抗匹配、数据传输时序及信号完整性的关键作用。当数据从控制器传输至DRAM芯片途中,经过总线传输线路后,往往因终端阻抗无法匹配而产生信号反射现象。ODT的主要功能便是依据数据传输时钟信号或初始化参数,对终端阻抗进行精确调节,以实现与总线特性阻抗的完美契合,进而消除信号反射,保证数据传输的稳定性与可靠性。

动态ODT与静态ODT比较

动态与静态ODT皆具备优劣势。前者可依据实际传输状况,实现实时调配以满足各类工作频率及负载环境之终端阻抗匹配;后者表现为稳定性高且可靠性强,其终端阻抗值于初始化阶段即已设定完成,毋须额外能耗。最终选择何种ODT类型,应视具体运用环境以及性能需求而定。

DDR3 ODT参数配置

在运用DDR3内存在系统运行中,进行有效的ODT参数设置对保持稳定与提升性能显得尤为关键。常见的需考虑因素有:动态ODT启动控制、末端电阻设置以及驱动力度调整等。通过精确调整此类参数能够改善总线传输表现、降低能耗损耗,从而充分挖掘DDR3内存的性能潜能。

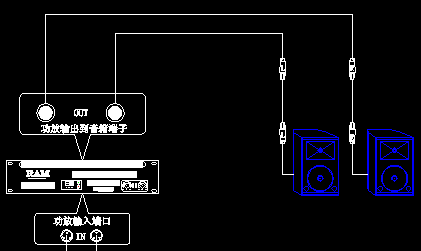

DDR3 ODT在系统设计中的应用

在计算机构架设计领域,DDR3 ODT技术广泛应用于提升内存子系统效能与稳健性。通过精准调控ODT参数、精选适用类型的ODT及精良布线设计等途径,能够成功应对信号完整性难题,降低电池消耗,进一步增强全系统绩效。因此,在系统构建过程中充分考量DDR3 ODT特性,对保障系统稳定运行具有关键意义。

未来发展趋势与展望

伴随着科技持续进步和市况需求改变,DDR3内存这一已臻完善稳健的产品仍具广阔使用前景。预计将来,我们会在保持现有的技术领先地位之上,对DDR3 ODT技术做更细致的优化,提升其带宽速度并减少能耗。同时,面对新一代内存标准如DDR4、DDR5的逐步推广,如何将ODT原理与新兴技术发展趋势相融合,也是未来研究的重要课题。