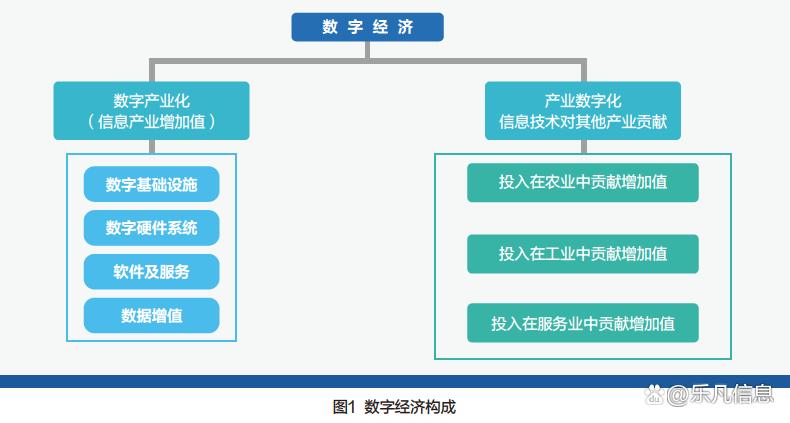

身为嵌入式系统工程师,我对此话题——ZynqPL读取DDR3——深感兴趣。在如今数字化日新月异的环境下,Zynq系列芯片凭借其强大的可编程逻辑单元(PL)及处理器系统(PS)融合之优势,广范应用于嵌入式领域。DDR3是高效能存储器的代表,引入ZynqPL后,系统能享有更大存储空间及更迅捷的数据传输速率。本篇文章将详细阐述ZynqPL如何读取DDR3,涵盖硬件设计至软件编程等多重角度。

1.DDR3内存概述

首先需明确,DDR3内存为一款具备双倍数据传输率的DRAM(动态随机存取存储器),相较DDR2,其具备更高的工作频率及更低的能耗。以众多存储芯片构成的DDR3,每个芯片内含多组存储单元与接口电路,广泛运用于嵌入式系统的程序储存、数据管控及临时信息处理等方面。

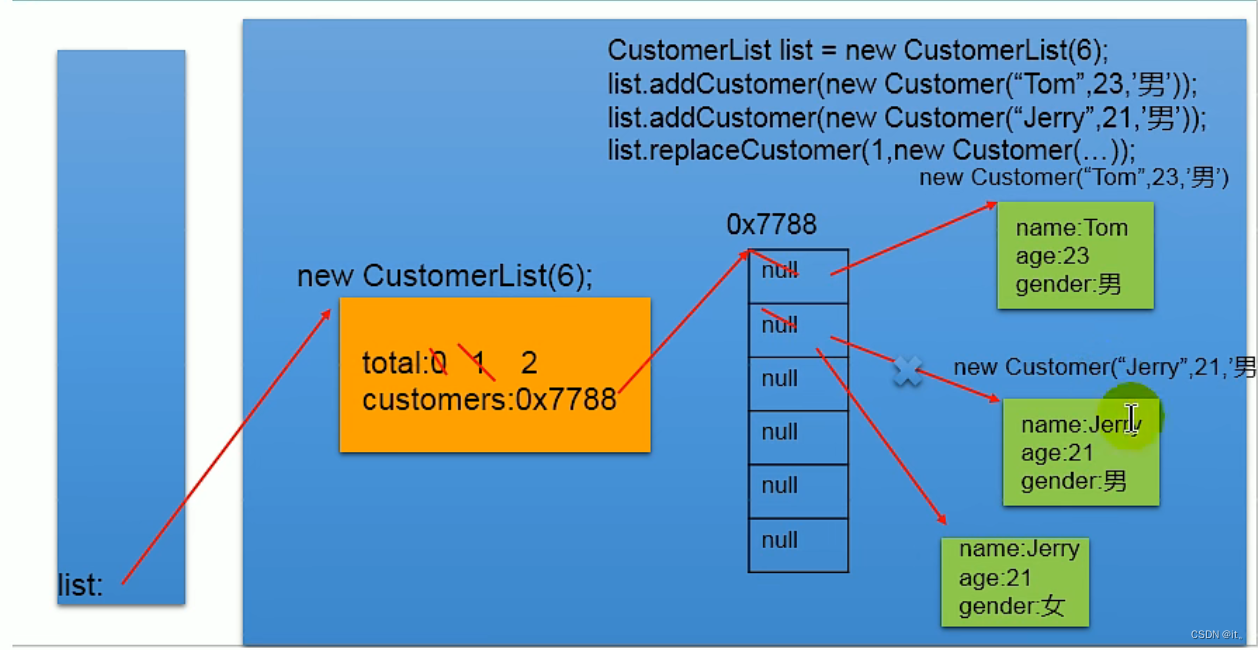

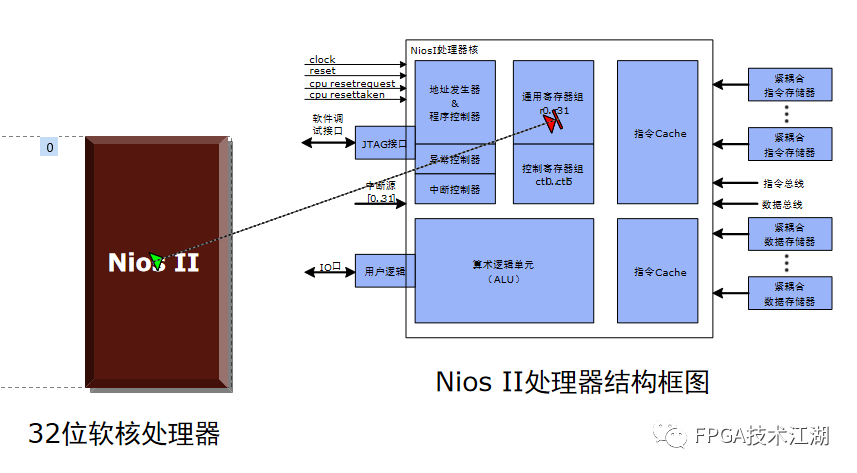

Zynq芯片中的PL部分为用户提供了灵活可编程的逻辑单元,用户可利用FPGA逻辑实现不同需求的定制化功能;而PS部分则囊括了内核处理器及各类外设接口等重要组件。通过精心调整和架构,PL与PS间的数据交互方式得以优化,从而实现高效率的数据处理和传输。

2.ZynqPL与DDR3连接

同时,为实现PL与DDR3的顺畅链接,需对时序匹配和信号稳定性格外关注。采用信号线路合理排布以及引入阻抗匹配电路等措施,可显著降低信号传输延时并提升系统稳定性。

3.数据读取流程

成功构建PL至DDR3的连接通道后,即可开始执行数据读取环节。首先,需通过软件驱动或者应用程序来操控DMA控制器,驱动其依照预先设定的参数进行数据传输,并将读取得来的数据存储至预定地点。

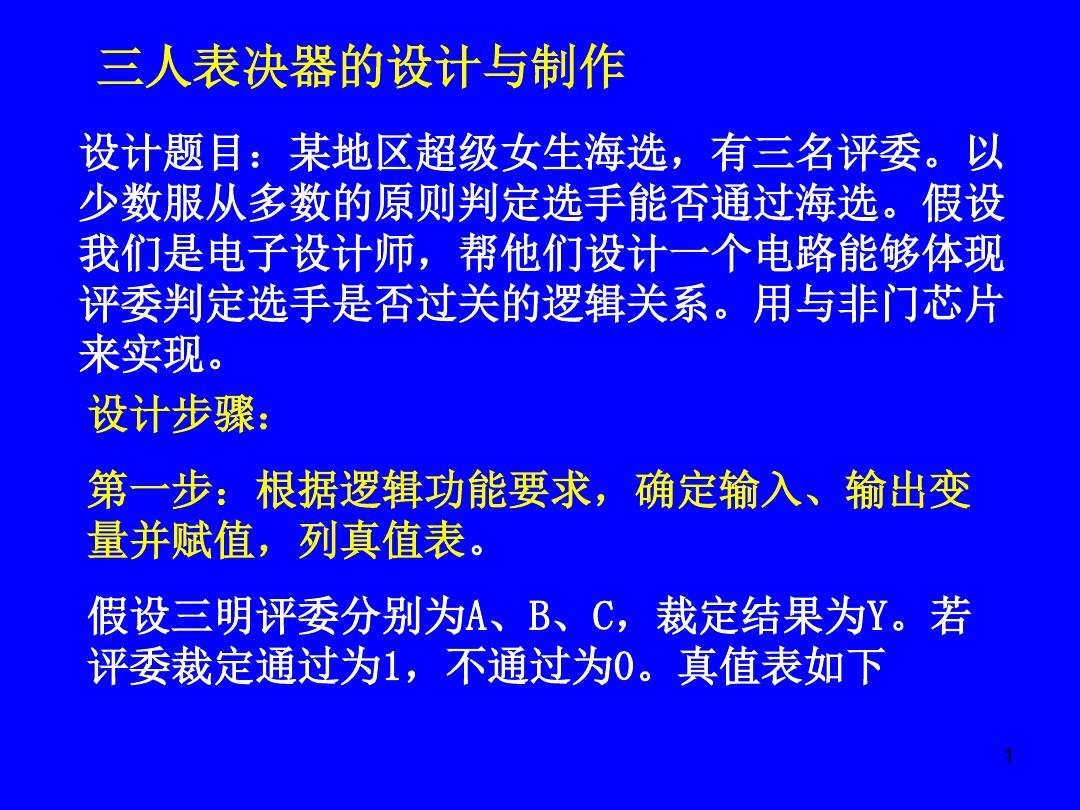

在硬件方面,恰当的逻辑电路设计成为提升数据读取效率的关键。其中,状态机、缓存区以及地址解析器等模块共同协作,顺利从DDR3内存获取所需的数据。

4.数据处理与应用

成功完成DDR3内存数据提取后,便需着手对其展开深度处理与运用。这包括但不限于数据解析、算法运算、图像处理等复杂工序。借助Zynq芯片的优势,我们能够运用浮点处理器(PL)的高度灵活性以及现场可编程门阵列(FPGA)的强大逻辑功能,构建各类定制化算法加速器或硬件加速模块。

依靠数据处理算法的硬件逻辑实现,PL环境中的计算速度得以极大提高;配合适当的PS驱动程序及应用程序,便可充分发挥硬件加速模块的潜能,实现最终的功能运行效果。

5.性能优化与调试

实践过程中,为确保系统表现的最优性,需实施必要的性能优化与调试策略。通过精心设计硬件电路架构,优化软件算法逻辑及参数配置等措施,实现系统整体运行效能提升。

此外,在调试环节,我们常面临如时间顺序波动引发的读写误差,以及DMA传输故障等复杂场景。为解决这些问题,需借助硬件与软件调试工具,对问题进行系统化分析与诊断,以找出并根治源头。

6.实际案例分析

本文旨在深入剖析ZynqPL读取DDR3的技术原理。末尾,结合一个实际案例详述从设计至调试的全套流程,以及实现期间所遇见的难题及应对策略。

7.结语

通过深度探究ZynqPL读取DDR3的技术原理,我们能够更加深入地理解这项技术,并能更好地指导在实际项目中的运用方法。未来,随着数字技术持续进步及不断创新,预期ZynqPL与DDR3的紧密结合将为嵌入式系统市场带来更多意想不到的惊喜。