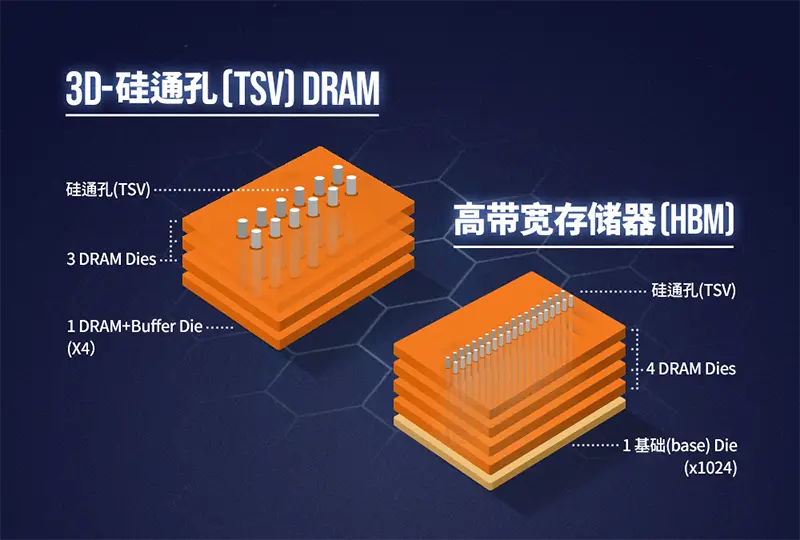

1.DDR3内存概述

DDR3内存作为典型的动态随机存取存储器(DRAM)之一,具备高速且高容的特性,广泛运用于各种计算设备之中。其快速的处理器间数据传输速率极大提升了系统运行效率,因此成为现代电子设备的首选。将此内存整合至Zynq芯片,可为嵌入式系统赋予更强的数据处理能力。

DDR3内存具备更高的运行频率与更低的电压需求,对电路设计提出了更为精确严谨的要求。在Zynq芯片的应用中,要深刻理解并妥善运用DDR3内存的特性和运作机制,进而确保电路设计达到预期效果。

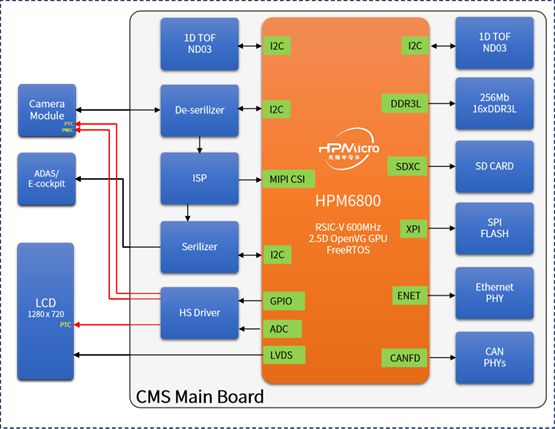

2.Zynq芯片概述

Xilinx的ZynqSoC融合了ARM处理器及可编程逻辑,结合了二者的优点,适配各种嵌入式需求。其核心理念在于提供高度灵活性与出色性能,因此在嵌入式系统设计范围内广受好评。

搭载了DDR3内存的Zynq芯片能大幅提高系统存储容量与数据传输速度,从而优化系统性能。因此,在设计ZynqDDR3电路时,需深入掌握其架构及特性,以确保达到最优效果。

3.DDR3电路设计考虑因素

在进行ZynqDDR3电路设计时,需要考虑多个关键因素:

-时序规定:DDR3内存在时钟、延迟、预充电等环节有严谨的需求。设计过程中务必保证所有信号符合时序规定,防止数据传送出错。

-信号完好性:确保信号传输未受干扰且能准确无误地达到预定设备。需注重信号线的长度与阻抗匹配问题。

-电源分布原则:鉴于DDR3内存对电源稳定性有较高需求,故需合理规划电源分布策略,并合理配置相应滤波器及去耦电容。

-电路板设计:良好的电路板设计可解决信号串扰和噪音干扰问题,进一步提高系统效率。重点关注差分对与接地线路规划等因素。

在设计告竣之后,进行仿真验证能够有效地揭示潜在问题,并实现及时的修改和完善。

4.DDR3时序控制

DDR3内存因工作频率较高,时序控制显得尤为重要。ZynqDDR3电路设计需参照规格手册设定相应参数,如读写延时、预充时间及时钟频率等。

合理设定的时序控制参数,能保证各信号在数据传送过程中的同步性及在恰当之时到达指定设备,提升系统稳定性与可靠性。

5.PCB布局与走线规划

优越的PCB布局乃保障DDR3电路稳定运行的重要因素。面对ZynqDDR3电路设计,需着重关注如下事项:

-差分对长度匹配:保证差分对长度尽量相等,避免信号失真;

-地线规划:合理规划地线走向,并减少地孔数量;

-确保信号线长度的均匀性:为了消除因长度不均衡而引发的信号同步误差,力求使各信号线等长。

-降噪处理:加入适当的降噪元件和去耦电容,减少干扰。

严谨的PCB布局与布线设计有助于控制信号干扰,增强抗干扰性,从而确保系统正常稳定运转。

6.供电系统设计

供电方案设计系ZynqDDR3电路精粹之一。鉴于DDR3内存对稳压供电需求苛刻,供电不稳或异常波动皆有可能引发数据传输误差乃至系统崩溃。

为了确保供电系统稳定可靠,在设计过程中需要考虑以下几点:

-设计合理的供电网络结构;

-添加适当数量和类型的去耦电容;

-考虑功率分配均衡问题;

-确保供应电压符合DDR3规格要求。

适当规划和配置电源系统能显著减少能耗损失、增强系统稳定性能及保证数据传输无碍。

7.仿真验证与调试

在ZynqDDR3电路设计顺利完成之后,接下来的关键步骤是仿真验证与调试。借助仿真工具的强大功能,我们能够及早探寻可能存在的问题,并迅速为之修正以保证系统的稳定运行。

在仿真验证过程中可以重点关注以下几个方面:

-时序约束是否满足;

-信号完整性是否良好;

-供电系统是否稳定可靠;

-PCB布局是否合理。

凭借严谨的模拟验证与调试,我们确信ZynqDDR3电路设计已完美迎合了需求且可持续地高效稳定运行。