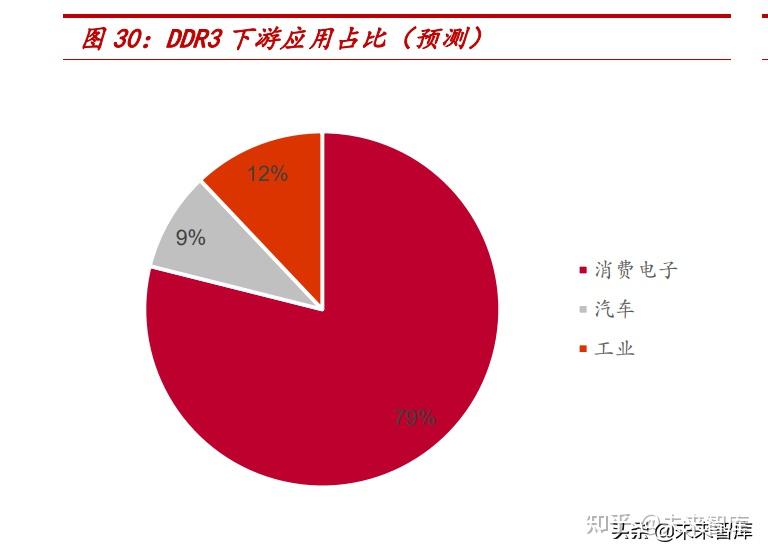

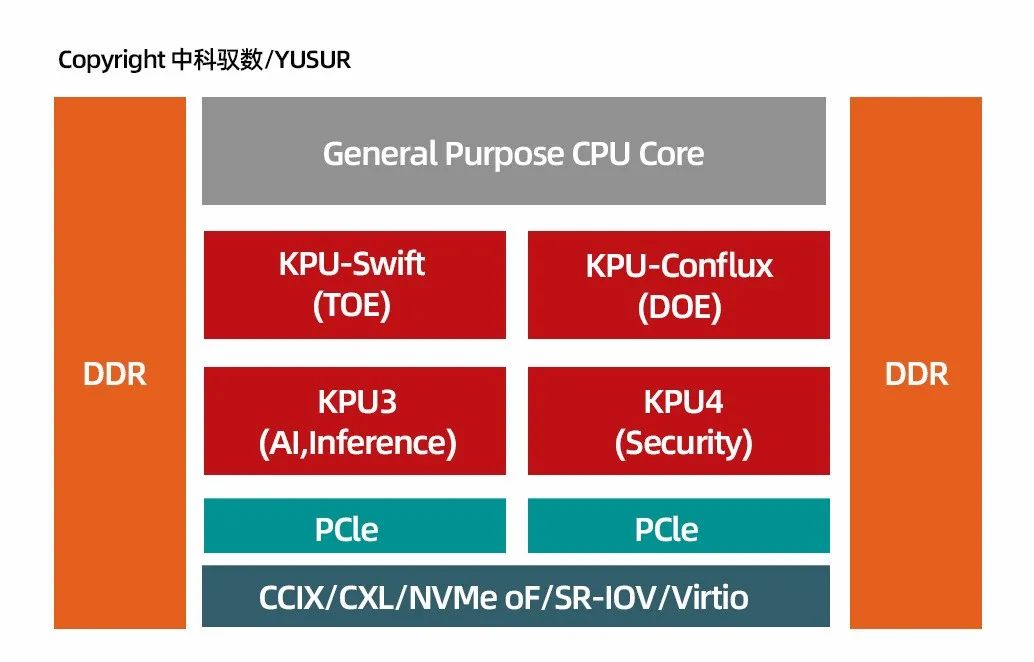

数字设计中的DDR(双数据速率)环节,对提升系统性能,节约能源以及合理利用资源起到关键作用,这涵盖了包括数字电路、逻辑设计及时序调控等多方面。现今电子产品中,DDR存储器已成主流配置,其质量与效率直接关系到整体系统性能。因此,电子工程师和计算机科学家需深入掌握并灵活运用DDR技术。

在执行数字设计DDR任务中,需关注各种因素如时序控制、数据传输速率、能耗优化及信号完整性等。合理制定DDR的数字设计策略有助于大幅降低系统能耗并提升数据传输效率,同时确保数据的可靠性与稳定性。因此,深入理解并熟练运用数字设计DDR的理论与技术对设计高效能、低能耗的电子系统具有关键意义。

时序控制在数字设计DDR中的应用

在数字设计DDR体系结构中,时序控制尤为关键;其核心在于对时钟信号的产生、同步以及延展等过程的精确把控。数字化集成电路的运行离不开时钟信号,它通过精准协调各部分节奏,确保数据于适当时刻得到准确的读取及记录。特别是对于DDR存储设备来说,时序控制的精度显得更加重要,因为它将直接决定读写操作的可靠性和高效性。

基于恰当地设定时序控制参数,可精准掌控存储器读写行为,防止数据混淆及遗失。与此同时,高速数据传送过程中的优良时序控制能保障数据信号持续稳定与完整,避免数据误传现象。由此可见,在数字设计DDR流程中,精心设立并严格审查时序控制参数至关重要。

数据传输速度与带宽优化

在数字设计DDR流程中,提升数据传输速率与带宽尤为关键。为应对日益增长的内存带宽需求,优化数据传输速度已成为急待解决的课题。合理选择总线结构、调整存储器访问方式及优化布线规划等策略,均可显著提升系统数据传输速率与带宽。

除了硬件层面对数据传输速率的优化,软件上,通过精密编写驱动程式和优化内存访问方式同样能提升整个系统的性能表现。因此,分析和优化数字设计核心DDR时,需全面兼顾硬件及软件两大层面因素,并依据实际应用需求进行精细调整。

功耗优化在数字设计DDR中的应用

伴随着移动设备及物联网设备等低功耗领域的日渐繁荣,如何在DDR(数字设计)环节中实现高效低能耗至关重要。这其中包括电路结构设计、工作模式选取以及节能算法运用等多重因素。通过选用低功耗元器件、优化电路排布并精确调整工作模式,可显著降低整体系统能耗。

数字设计DDR过程必须重视能耗与性能间的均衡。降低能耗并非以牺牲系统整体性能为代价,而是在确保系统稳定运行的基础上,寻求最低能耗的复杂且具挑战性任务。因此,在实施能耗优化时,需综合考量系统需求,寻觅最优平衡点。

信号完整性与抖动分析

高速信号传输中的信号完整性,即保证信号波形无失真、稳定,防止出现波动或变形。抖动现象实质上是由多种原因导致的信号波形变化。在数字设计(如DDR)环节中,深入理解并处理好信号完整性及抖动问题,对提升整个系统的稳定性和可靠性至关重要。

为解决信号完整性问题,可借助仿真工具对信号波形进行分析,从而避免出现如串扰和反射的不良影响。此外,应特别注意抖动问题,可利用眼图分析等技术估计抖动状况,再依据分析结果调整设计参数,以保证信号质量达标。

自适应均衡技术

自适应均衡技术被视为解决信道损耗及噪声干扰引发信号畸变的高效策略。在DDR数字设计过程中,这类现象导致信号品质降低,从而对整个系统表现产生影响。借助自适应均衡技术,可实时调整接收端滤波器参数,提升信号质量并降低误码率。

自适应均衡技术依托数学模型及反馈机制,智慧调配滤波器参数以应对多变的信道环境。此项技术特别适用于高速信号传输领域,不仅可明显提高信号质量,更能增强体系稳定性与可靠性。

故障检测与容错机制

由于外部因素或设备本身的问题,数字设计DDR在实际运用中易受干扰。因此,故障检测及容错机制的重要性不言而喻。通过在设计过程中加入这两种机制,我们能实时监控系统运行状况,并对异常情况做出迅速反应。

故障检测包含硬件及软件两大层面。前者借助冗余元器件或专用监测电路;后者通过编写异常处理程序或引入状态监控模块达成。整合运用这两类方法,构建完善的故障检测与容错机制,对于保障系统稳定至为关键。