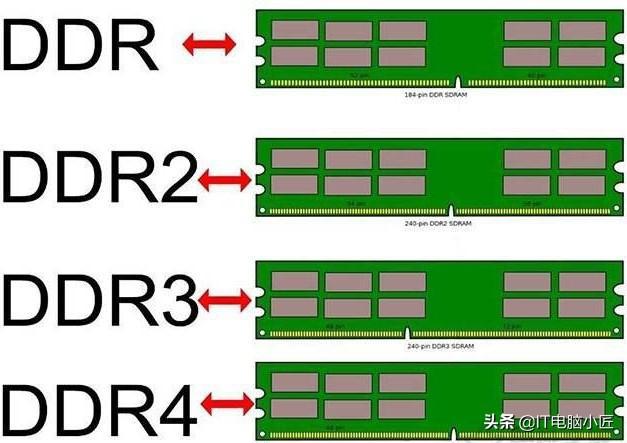

DDR内存测试时序在当代计算机工程领域具有举足轻重的地位。通过精细剖析与精炼优化这一环节,我们有望提升内存访问效率,缩短等待时间,进一步提升整个计算机系统表现。本文将以DDR内存基本原理作为起点,层层深入解析测试时序诸多问题,为广大读者奉上一场丰富且深入的DDR内存测试时序旅程。

DDR内存基本原理

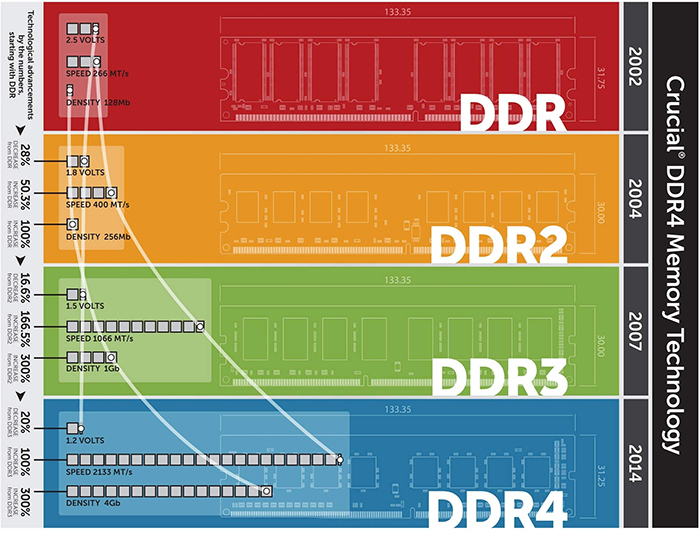

DDR(DoubleDataRate)内存,因其具备双倍数据传输速率而成为当下计算机体系中主流之选。与传统的SDRAM相比,DDR内存通过每周期双次数据传输提高了数据效能,其运作原理涵盖数据传输、时序调控及电源管理等多层面。其中,时序调控尤为关键,它直接影响着存储器在各类操作中的响应速度和稳定性。

时序控制在DDR内存测试领域中占据重要地位,包罗万象,涵盖了多项复杂的环节,如读取/写入、预充电以及刷新等时序特征。精准地掌控与调整这些时序,可显著提升DDR内存的性能及稳定性,确保计算机系统能稳定且高效运转。

读写时序优化

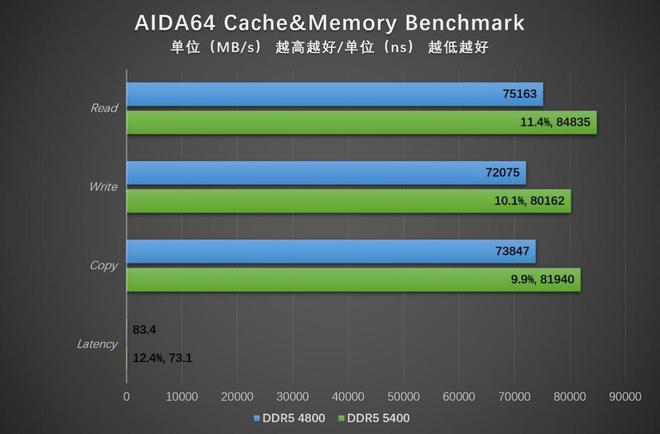

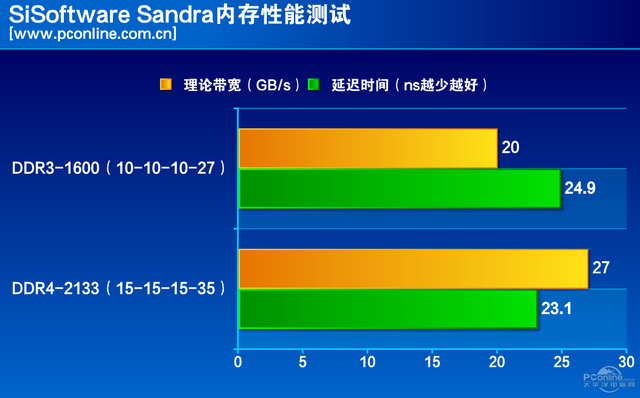

读写时序乃是DDR内存测试过程中的关键要素。在这一阶段,内存控制器需严格把控数据传输的节奏与速度,从而保证数据的可靠性及稳定性。读写时序的优化涵盖了延迟时间的微调、时钟周期的协调以及数据线路的精准校正等众多细节。精妙地调整诸如此类的时序参数,便能显著降低读写操作的延迟,大幅提升数据传输效能。

在优化DRAM内存读写时序过程中,必须重视内存芯片规格与工作环境,并结合系统整体结构及性能水平来制定合适的读写策略和优化措施。根据不同应用需求与情境,选择最优读写时序策略与优化方案,实现最佳性能效果。

预充电时序调整

预充电时序乃DDR内存测试过程中至关重要的一环,其作用在于规划内存芯片于读写操作之前的准备阶段及其状态。而其调整措施涵盖预先充电电压设定、充电时间调控以及电流调整等多重环节。精细调节预充电时序不仅能显著降低读写能耗与延迟,更可提升整个内存系统的性能表现。

在施行DDR内存预先充电时序调节时,需着重考量内存控制器与内存颗粒的兼容度及系统电力供应之稳固性及负荷能力。透过适度调整预充电时序设定,以达致内存系统效能与稳定度的最优状态,从而提升计算机集成操作的整体效率。

刷新时序管理

DDR内存运行中的刷新时序,是确保稳定可靠性能的关键环节之一,其设定直接影响着刷新的间隔与次序。此过程涉及到刷新周期的设定、刷新指令的传递以及刷新执行的调度等等。科学的刷新时序管理,有助于提高内存系统的稳定性,防止数据遗失及系统崩溃现象的出现。

在实施DDR内存刷新时序控制策略中,需着重考量内存芯片的工作条件及系统负荷,且结合实际使用环境与需求。通过精确调整刷新时序参数,确保内存系统达到平衡稳健状态,进而提升计算机系统总体的可靠性与性能水平。

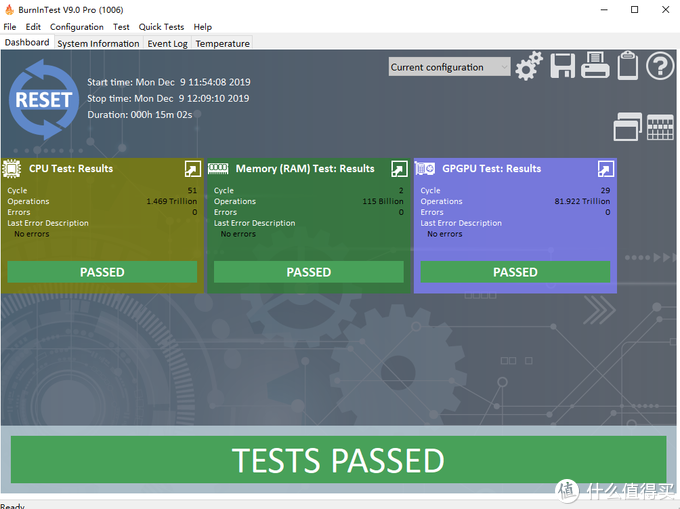

时序测试工具

时序测试工具在DDR内存测试中起关键作用,主要用于时序分析与优化。其中包括逻辑分析仪、示波器及信号发生器等多元设备及软件。这类工具可助力工程师即时分析内存时序信号的波形和参数,精准定位并修复时序问题,从而有效提升测试效率及其准确性。

在挑选和应用时序测试工具时需因地制宜,充分考量测试要求与预算限制。在对DDR内存进行时序分析及优化过程中,可融合多种时序测试工具的优势,从而获取更为全面、精确的测试成果以及优化策略。

时序优化策略

时序优化策略在衡量DDR内存测试质量上发挥着关键作用。合理利用该策略可提升内存系统性能与稳定性,降低能耗及成本。具体措施涵盖时序参数微调、控制优化以及测试强化等多方面。

在制订并执行时序优化策略过程中,务必综合考量内存颗粒规格及工况、系统实际使用环境、性能需求等多因素。科学筛选与整合时序优化措施,得以确保内存系统卓越性能与稳定表现,提升整个计算机系统运行效能与用户体验。

未来发展趋势

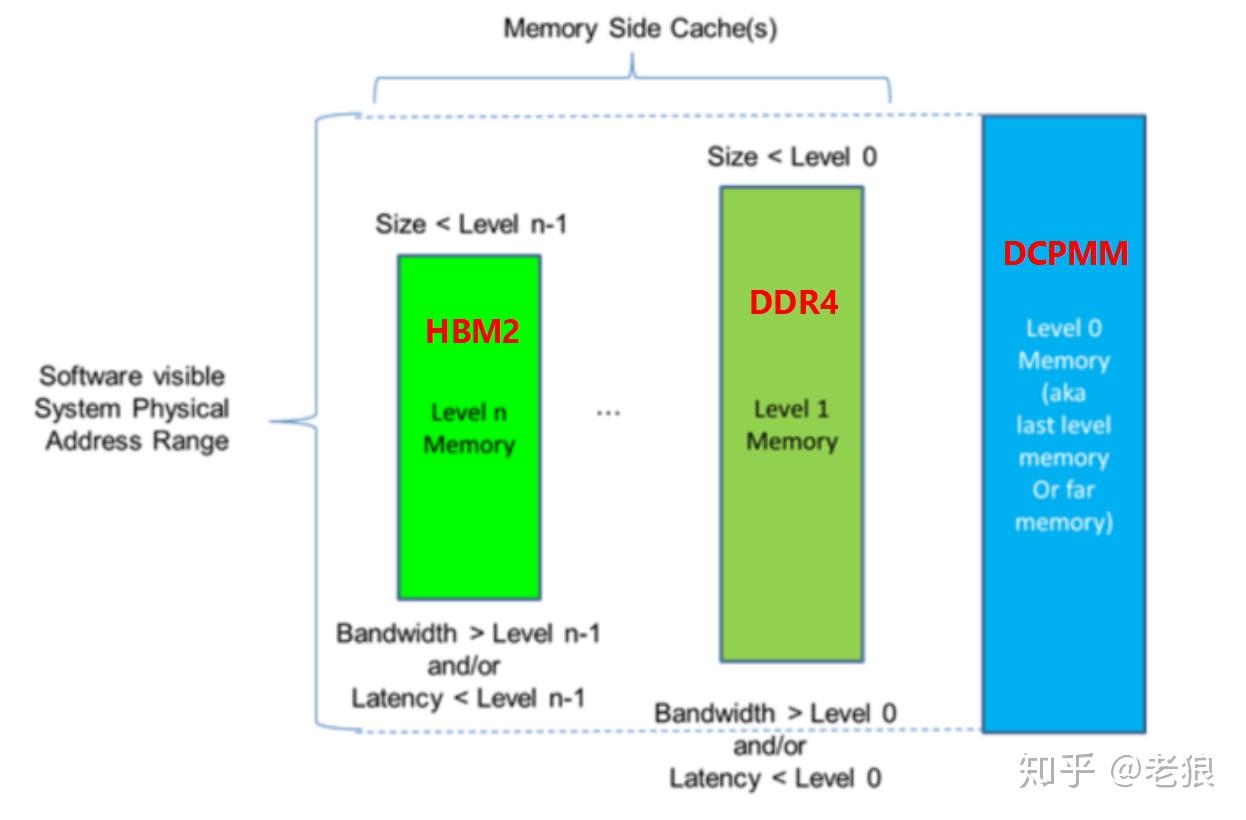

随着计算机科技不断演进,DDR内存测试时序亦随之创新及突破。展望未来,DDR内存测试时序更注重数据传输效能与能源消耗的控制,以满足不断变化的使用环境和需求。但同时,新型存储技术不断出现并广泛运用,为DDR内存测试时序带来诸多全新挑战与商机。

未来的发展趋势包括但并不局限于新式存储技术的引用、时间序列测试设备的智能化以及精炼的时间序列优化策略等多个领域。通过持续创新与发展,DDR内存测试的时序层面必将为计算机系统带来更高的性能提升和更低的能源消耗,引领整个计算机行业迈入更为繁荣且稳定的发展轨道。