随着信息化进程的加速推进,存储技术亦不断创新突破。DDR(DoubleDataRate)与eMMC(embeddedMultiMediaCard)作为当前主流存储技术的代表,肩负起海量数据传输与保存的重任。本文旨在全面解析DDR及eMMC的构造与运行机制,揭示其神秘面纱背后的技术奥秘。

DDR存储原理

DDR(DoubleDataRate)是高速存储器技术之一,其复杂且精细的内构与运作,要求我们进行深入理解。首先,我们需先对DDR存储的内部构造有个清晰认识,即包含了存储晶片及控制器两部分,前者乃是储存资料的关键所在,后者则负责监管数据的读写操作过程。

DDR存储器内的数据交换依靠芯片里的存储单元,此存储单元由晶体管及电容构成,利用电压改变反映数据储存情况。在读取过程中,控制装置依照地址信息传送至存储芯片,随后定位并转译存储单元电压至数字信号输出。相反地,写入数据操作时,控制器先将数字信号转变成电压信号,然后写入为该存储单元预先设定的位置。

在此基础上,DDR存储器采纳了双数据速率技术,该技术可在单个时钟周期内传递两遍数据,显著提升数据传输速度并增强存储能力。借助于此项技术,DDR存储器能够在信号波形的上升沿和下降沿均进行数据传输,使得数据读取与写入过程更为迅捷。

DDR存储器主要依靠时序控制与信号调控实现运作。时序控制用于精确协调各存储单元操作,确保数据读写无误;信号调控则致力于调节数据传输时的电压与时钟信号,保障数据传递的稳定可靠。

eMMC存储原理

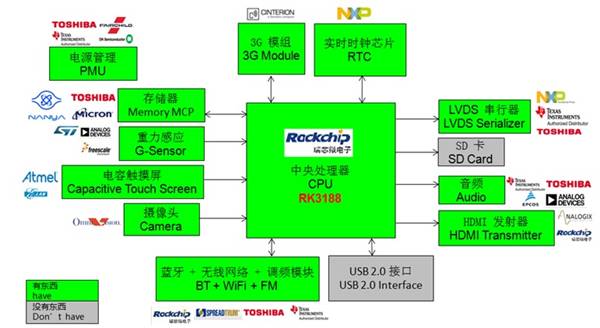

eMMC,即嵌入式多媒体卡,集存储与控制功能于一身,广泛运用于移动设备及嵌入式系统领域。解析eMMC存储原理,需结合其内部构造及运行机理两角度阐明。

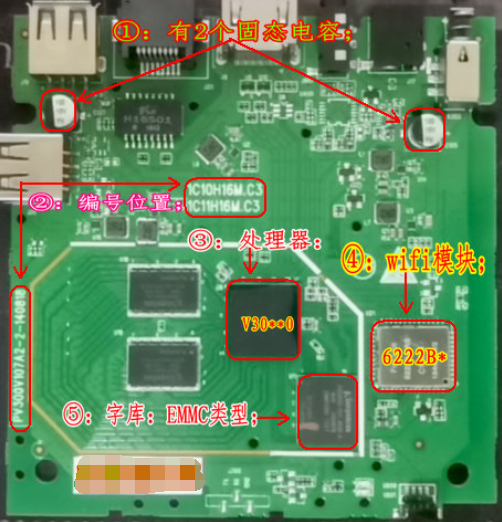

首先,让我们探讨eMMC存储器的内部构成。此存储器主要包含闪存芯片、控制器与存储管理器三部分。闪存芯片主要进行数据存储;控制器则是执行读写指令的重要机器;存储管理器则在不同程度上对闪存芯片内的空间进行调配与分配。

对于数据读写功能,eMMC存储器运用了NAND闪存技术,这是一种高效率、大容量的非易失性存储方式。eMMC借助控制器,使用特定的命令和地址信号完成闪存芯卡的读写动作。阅读数据时,控制器向闪存发出读取指令及地址信号,随后将获取的数据传送至存储缓冲区,再经由接口传送到外部设备。而在写入数据阶段,控制器先将待写入的数据送入存储缓冲区,接着向闪存发出写入指令与地址信号,最终将数据写入指定的存储单元内。

在数据读写之外,eMMC存储器具备多项性能如数据管理及错误检测与修正等。其中,存储管理器致力于管理闪存芯片内部存储空间,涵盖了块管理、擦除处理以及写入能力平衡等环节;另一方面,错误检测与修正功能则主要用于侦测并修复存储过程中出现的数据误差,从而确保数据的可靠性与完整性。

DDR与eMMC的比较

深刻把握了DDR与eMMC的运作原理后,我们得以对两者进行细致对比。首当其冲,就数据传输速率而言,DDR存储具备显著优势,更适合于追求高效性能的应用环境;相较之下,尽管eMMC存储的传输速度相对较慢,但由于其低廉的成本及高度集成性,使其成为受限于成本和能耗限制的理想选择。

在实际运用中,DDR存储器更适用于需要卓越存储性能的PC、服务器以及高端运算设备等领域;与此同时,eMMC存储则常用于移动设备、嵌入式设备以及物联网设备等对成本和能耗有所限制的环境。

相较之下,DDR存储器凭借其优越的可靠性与稳定性,使之适宜用在对数据稳定度有极高要求的场合;而尽管eMMC存储器在稳定性及可靠度方面稍逊于DDR,但在移动设备以及嵌入式系统领域内,仍能满足基本需求。

未来发展趋势

随信息科技持续进步,DDR及eMMC储存技术亦不断优化升级。从现状看,未来发展存在如下趋势:

加速:随着数据传输速度持续攀升,未来的DDR存储功能将愈发强大,以更好地应对日益繁重的数据处理压力。

低功耗特性显著:鉴于移动设备与物联网设备日益普及,未来的eMMC存储将更加强调低功耗及高度集成化,以适应电池续航能力及体积方面的严格要求。

多元化:未来的储存技术将呈现出更加多元的特点,其中包括采用新型材料与构造方式的存储设备,以期在各种应用环境中得到充分满足。

结语

通过本篇文章的解析,使我们能够更为透彻地理解DDR与eMMC存储器的运行原理。作为高速便捷的储存技术代表,DDR在个人电脑及服务器等领域具有举足轻重的地位;而集成度高效、价格实惠的eMMC存储器则在移动设备以及嵌入式系统中得到了广泛运用。展望未来,随着信息科技的持续进步,DDR与eMMC存储器技术亦将不断革新,为人们提供更为高效便捷的数据存储解决方案。

预计在未来的发展前景中,DDR与eMMC存储技术将会迎来哪些重大突破?而对于这些技术进一步的改进空间,我们又该如何看待呢?欢迎各位读者积极参与评论与探讨。