伴随着科技的飞速进步,嵌入式系统的需求日益显著。其中,DDR内存的引入堪称核心环节。本文将详细分析Zynq处理器如何接驳DDR内存,涵盖硬件设计与软件配置等多个层面,全面剖析这一复杂且关键的过程。

1.DDR内存简介

首先,让我们深入理解下DDR内存的定义和特性。DDR即为双倍数据速率,属于高速动态随机存储器(DRAM)的范畴。相较于传统的SDRAM,DDR内存利用了新的技术提高了数据传输速度,从而完美适应了现代嵌入式系统对于高效存储的实际需求。在众多嵌入式系统中,如网络设备、通信系统以及工业控制等领域,都能看到DDR内存的身影。

2.Zynq处理器概述

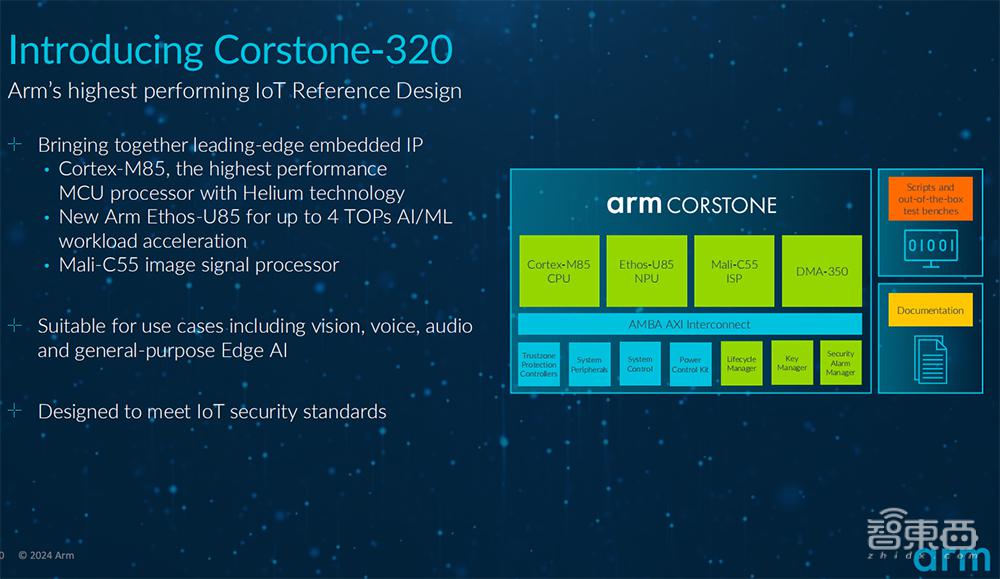

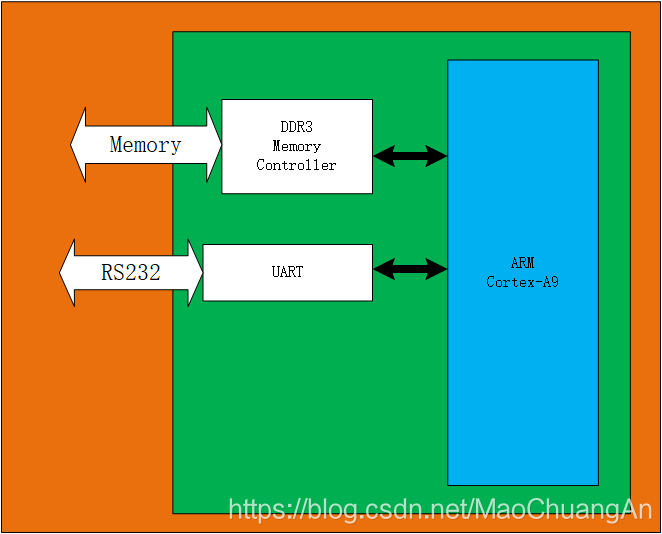

Xilinx公司研发的Zynq嵌入式处理器集ARMCortex-A9与FPGA技术优势于一身,展现出卓越的计算能力及高度的灵活性,该产品在各类嵌入式系统中的应用极为广泛,优异的处理性能以及高度的灵活性深受广大嵌入式系统设计师青睐。

3.Zynq接入DDR的必要性

诸多嵌入式系统需配备具备大容量与高速性能储存功能的器件以保存各类数据及程序,DDR内存恰能满足此要求,成为嵌入式系统主要存储设备。因此,将DDR内存与Zynq处理器紧密结合,将为嵌入式系统带来更为高效且稳定的存储解决方案。

4.硬件设计方案

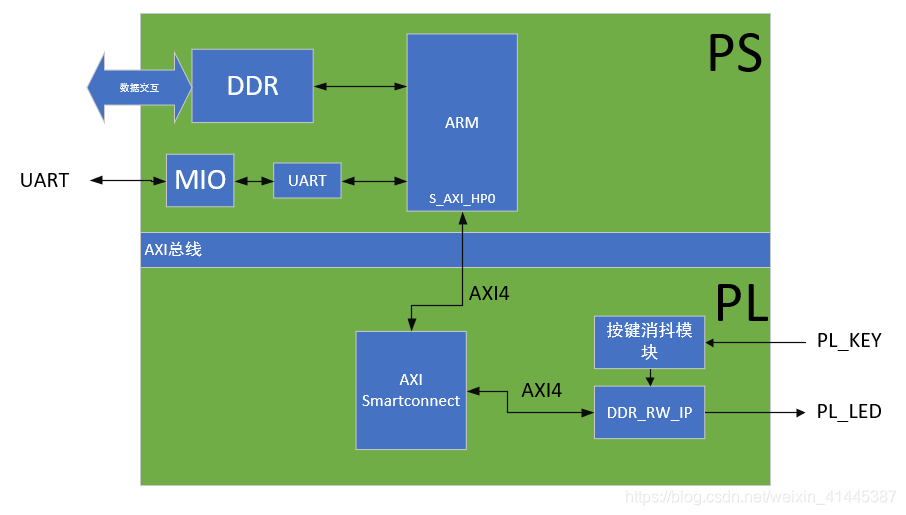

随后,本文主要探讨Zynq处理器与DDR内存在硬件中如何有效相连。首要任务是选择适当的DDR内存芯片,之后依据规格详细设计相关电路板。在此过程中,务必关注信号完整性和时序匹配等重要因素,以此保障Zynq处理器与DDR内存间数据传输的稳定性及可靠性。

硬件链接上,常运用高速串行接口(例如DDR3/DDR4)将DDR存储器与Zynq处理器相接,此类接口具备了高速度与低消耗的特性,以适应当今嵌入式系统对数据传输及能源需求的标准。除此之外,供电以及时钟同步等关键因素也不容忽视,以确保整个系统的稳定性及可靠性。

5.软件配置流程

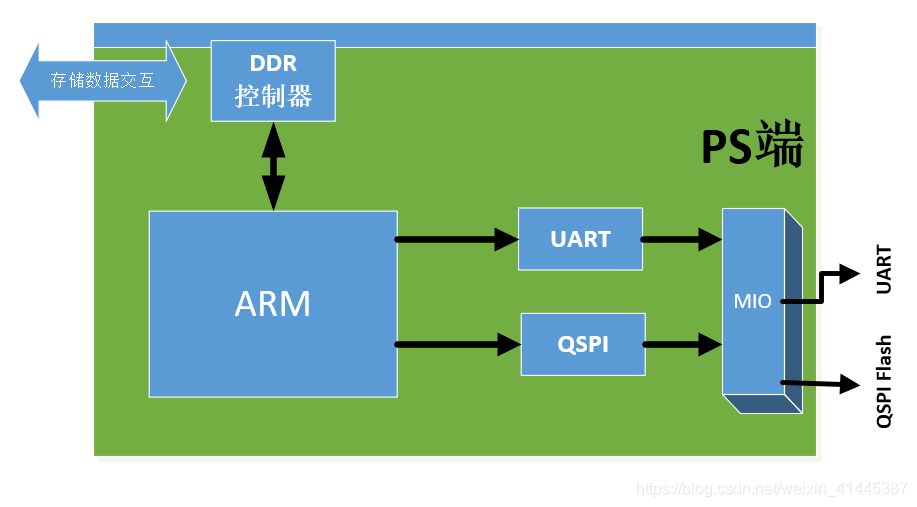

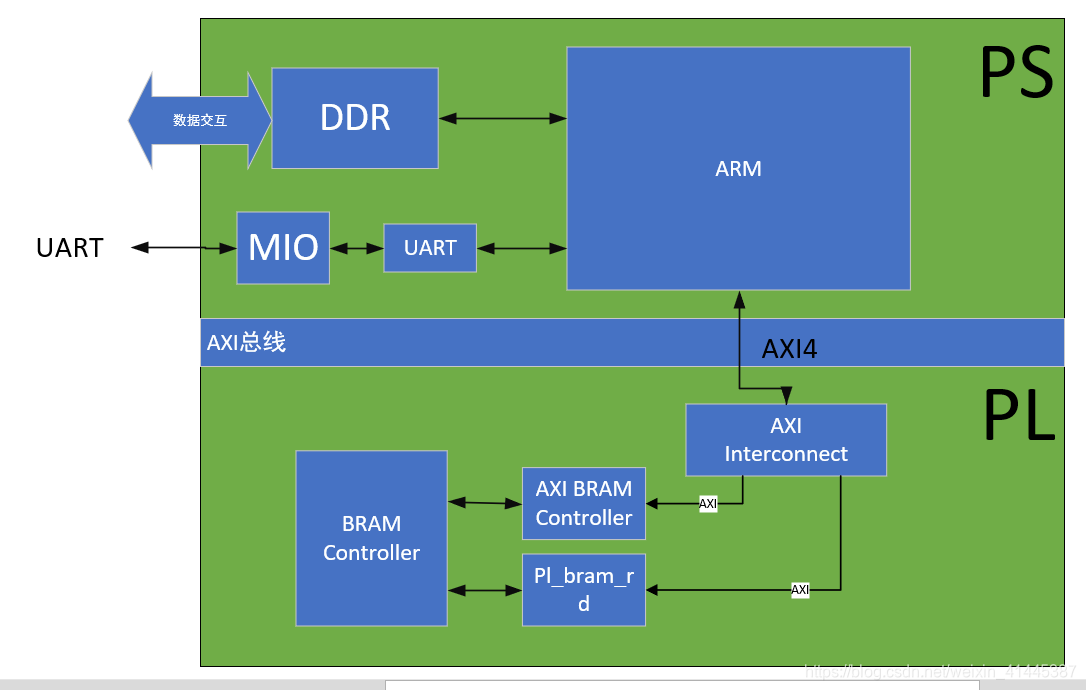

除硬件设计外,软件配置是实现Zynq与DDR内存连接的关键环节。使用Xilinx提供的工具(如Vivado)对Zynq处理器进行初始化和配置,确保正确识别并访问DDR内存显得尤为重要。

首要任务是在Vivado平台上建立新工程,选择Zynq处理器,参照DDR内存规范书设定其内部存储控制器的时序及地址映射等参数。紧接着,编写并编译适宜的硬件描述文件(如VHDL或Verilog代码),最终生成.bit文件。完成后,将此文件载入Zynq处理器,再运用C语言等软件进行编程,实现对DDR内存数据与程序的操作。

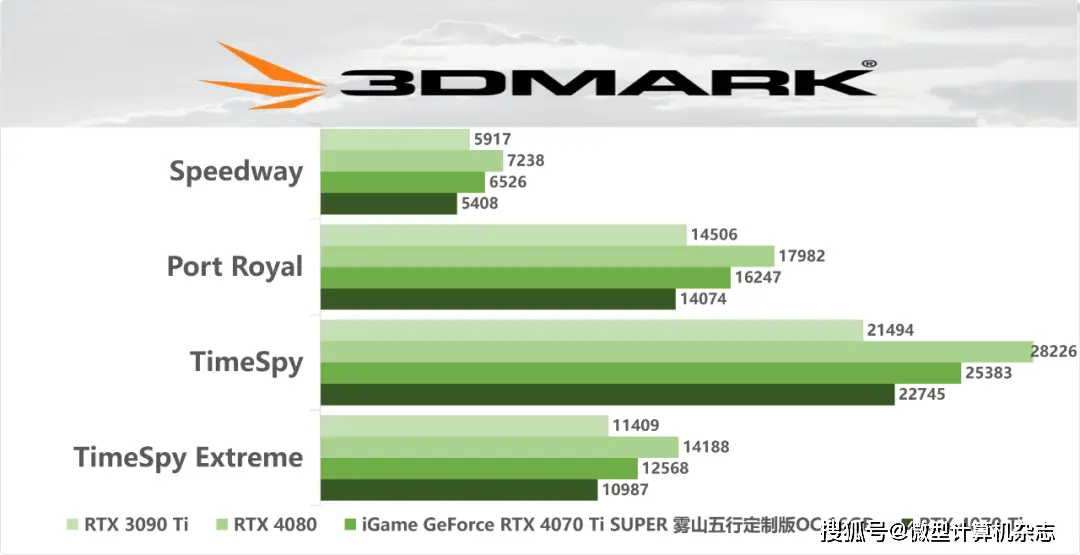

6.性能优化和调试技巧

实践中,为提升系统效能及稳定性,可实施性能优化与调试策略。如调整DDR内存时序参数,优化存储访问模式等手段,以提升数据传输速率及响应速度。同时,借助Xilinx提供的调试工具(如SDK),对系统性能进行深度分析并排除故障,确保系统稳定运行。

7.实际案例分析

本节将通过详尽案例阐述Zynq如何接入DDR内存。以一款典型嵌入式视频处理系统为例,我们将深入分析该系统的硬件架构及软硬件配置方法,并分享性能优化、调试策略等实用经验,以期助力广大读者深入理解并熟练运用这一技术。

经过深入研究发现,实现Zynq与DDR内存的接驳,不仅需要具备先进的硬件设计知识,还需对软件配置与系统性能调优提供深层次的理解。唯有如此,方能成功构建稳定可靠且性能优越的嵌入式系统。