身为电子工程师,面对纷繁复杂的电路设计及硬件研发课题,DDR(双倍数据率)内存因其普遍性而成为关键角色。尤其是其内部的行列地址线,更是设计者必须了解并掌握的设计要素。在此篇文章里,我愿意分享自己对DDR行列地址线的独特见解与体验,希望能为广大读者带来启示。

了解DDR行列地址线

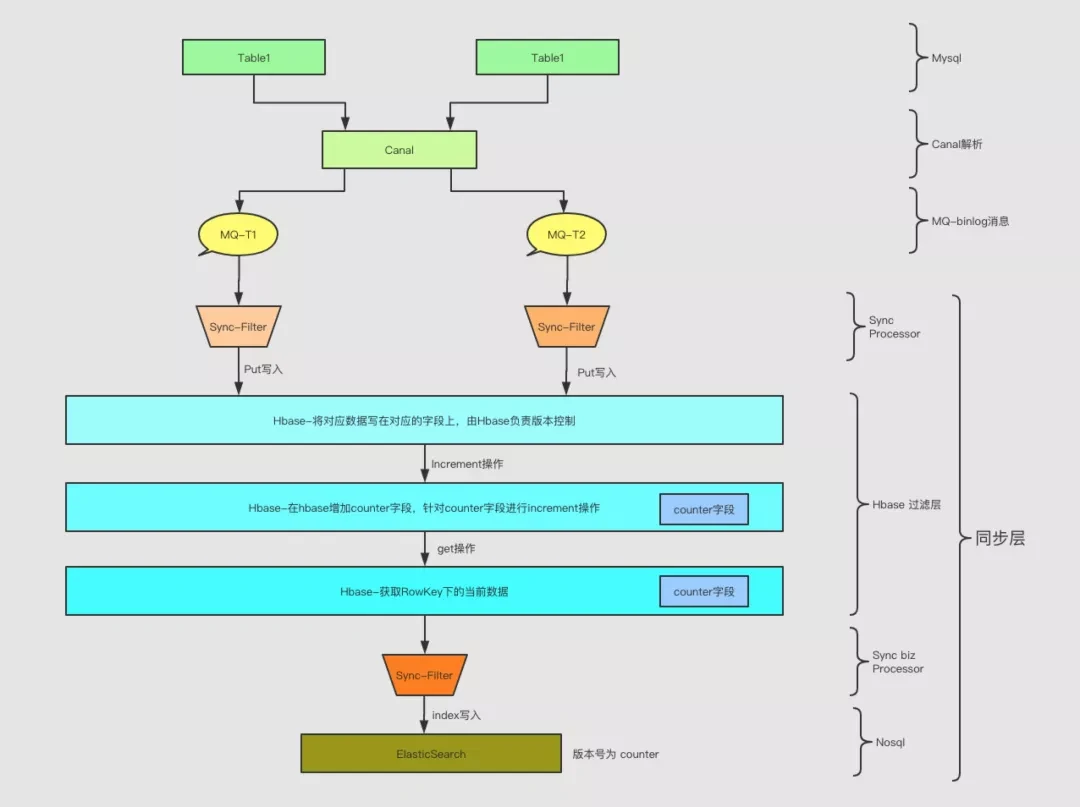

首先,让我们深度探讨一下DDR内存中行列地址线的关键原理。在这种内存模组中,行列地址线是决定访问哪个存储单元的核心因素。DDR内存以横纵方向将数据划分存储,行列地址线便起到指示相应行列的作用。总的来讲,行地址线决定需要读取的数据行,列地址线则指向欲读的数据列,二者共同决定了存储单元的精准定位。

DDR内存行列地址线数量受制于内存容量与架构。对于低密度DDR内存,可能仅需寥寥数根行列地址线;而高容值DDR内存唯有借助更为丰富的行列地址线方能实现更大存储空间。作为设计DDR内存控制器者,务必考量行列地址线总数及排布,以保证对存储单元的准确存取。

DDR行列地址线的工作原理

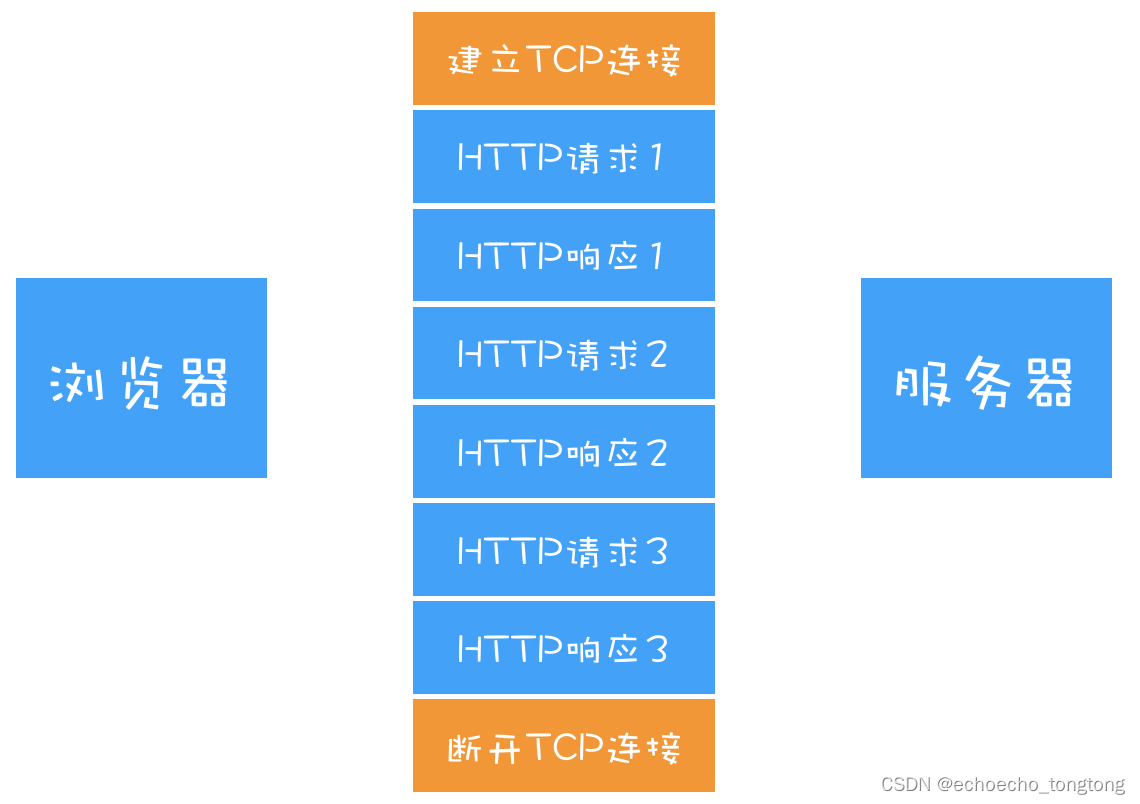

经过对DDR行列地址线基本理论的学习后,接下来我们详细探讨其运作机制。DDR内存通常分两步完成读写操作:预充电与访问。预充电阶段,内存控制器向内存芯片发出行列地址及预充电指令,此时内存芯片会将指定行的数据预先加载至内部输出缓存区,为后续读取做准备。

完成预充电后,即进入访问环节。在此阶段,内存控制器发送行、列地址以及相关读/写指令。紧接着,存储器依据接收的行列指示选定对应的存储元,然后将其内容上传至输出缓存器,以便内存控制器进行读取或写入操作。这一系列动作往往可以在短短数个脉冲周期内迅速完成。

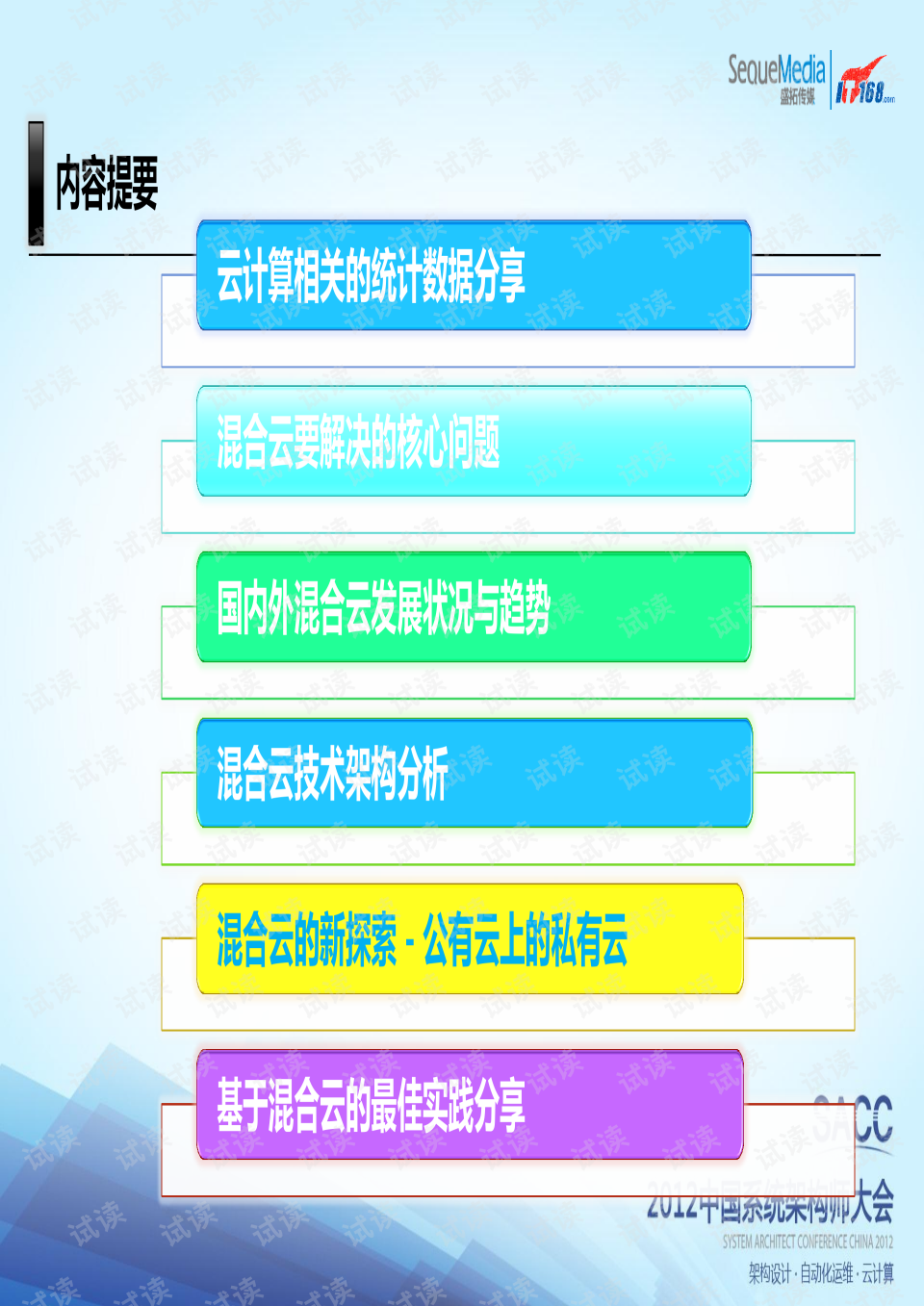

DDR行列地址线的设计考量

在DDR电路设计实践中,需全面审视多重制约因素。首要关注点即为布线长度及信号质量问题。鉴于DDR内存具备较高的运行速率,过长的行列地址线将导致信号传输速度与稳定性受损。故此,必须精打细算布线长度,采用最佳布局规划及信号层次化架构,从而保障信号的整体性能。

在此,必须充分关注供电及接地布线,因为DDR内存对其稳定性有较高需求,尤其是高频环境下。为了降低信号干扰与串扰,需提供充足的电源滤波与良好的接地衔接。因此,在制定DDR行列地址线路方案时,应严谨规划好这两者的分布,以保证内存正常运行。

需特别注意DDR内存的时序需求。DDR的读写速度常受预充、存取等时序因素影响。因此,在设计DDR行列地址线时,务必确保其符合内存的时序需求,防止时序违规,从而保障内存正常运行。

DDR行列地址线的故障排除

在电路设计及硬件开发环节,我们可能遭遇与DDR行列地址线有关的种种故障,多为信号完整性不佳、时序违规以及电源地线问题。针对这类状况,我们必须进行全面且精密的故障排查与调试工作。

在评估信号完整性的过程中,首要任务就是采集信号并进行波形分析。若测得信号波形存在问题,则可能由接线工艺欠佳或信号层布局不够科学所致。此时,可通过优化布设接线与调整信号层次结构以修复此类问题。

此外,还需检测时序是否达标。若是时序违规现象,多因时钟信号波动或传输延迟所致,可通过调整时钟源头与疏通信号通道予以解决。

在检修过程中,需重点检测电源与接地线之连接状况。若存在电源地线不良现象,有可能引发信号噪声及串扰等问题,从而干扰到DDR内存的正常运行。建议通过检验电源滤波器以及接地连结状态以排查并排除此类故障。

结语

在对DDR行列地址线的深入研究与剖析后,本人对DDR内存运作机理的认知又得到深化。行列地址线作为DDR内存的核心组件,其设计及调试对于电子工程学与硬件开发具有至关重要性。未来的职业生涯里,本人将会持续深研DDR行列地址线相关知识,以期提升自身的技术水准。