面对SOC芯片DDR测试这一富有深度且充满挑战的话题,作为资深芯片工程师的我深感其重要性及复杂性。在此篇文章中,本人将向各位读者阐述关于SOC芯片DDR测试的心得与经验,期望能为您带来具有参考价值的观点与灵感。

什么是SOC芯片DDR测试?

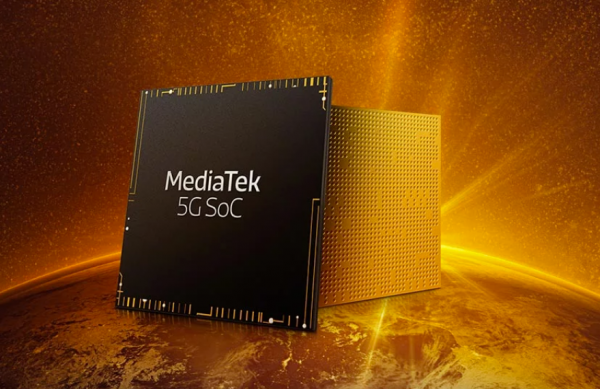

让我们先认识下何谓SOC芯片DDR测试。所谓SOC(SystemOnChip)芯片,是将处理器核心、内存控制器与外设接口等多种功能整合为单一集成电路的产物;而DDR(DoubleDataRate)内存,因其具备高速数据传输及低功耗特性,在各类计算设备中得到广泛运用。SOC芯片DDR测试,即对SOC芯片内的DDR存储器进行一系列严谨测试,以确保其性能稳定可靠。

在SOC芯片内,DDR存储器起到了举足轻重的作用,承担着临时储存数据的任务,对芯片整体运作速率与稳定性有着直接的影响。故此,进行DDR测试具有深远意义,有助于揭示潜在问题,加以迅速解决,从而保证芯片质量及性能。

DDR测试的关键技术

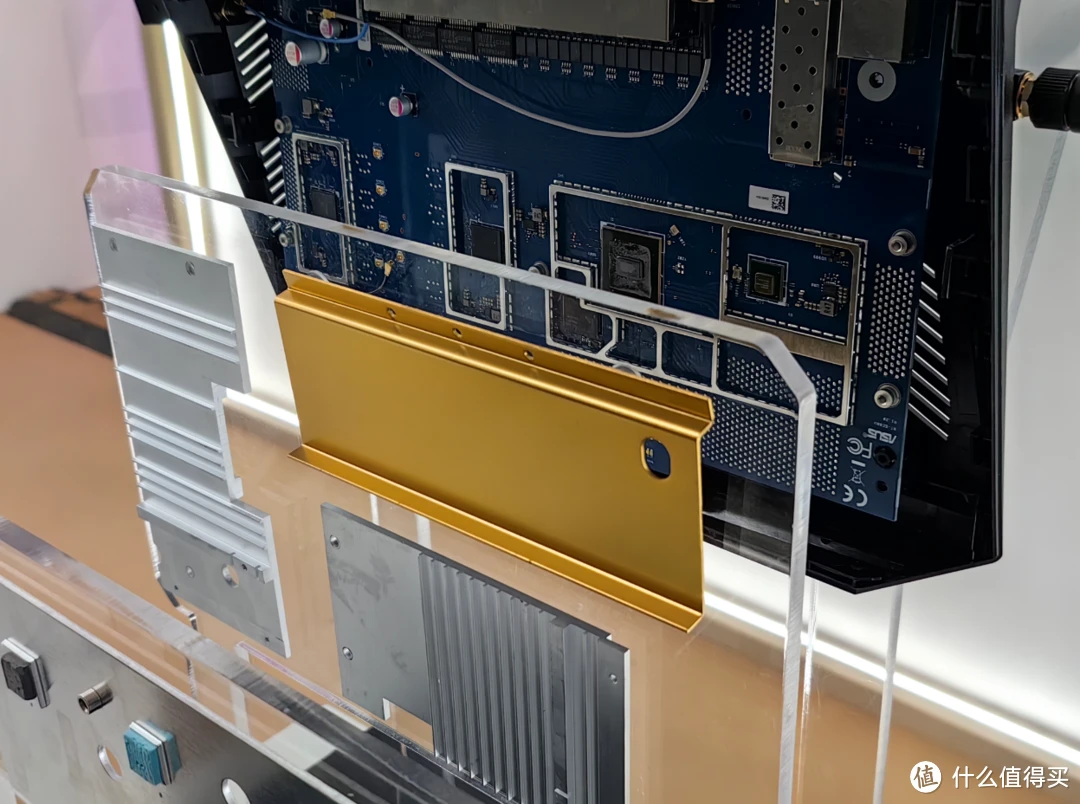

成功实施SOC芯片DDR测试,需具备诸多关键技能。首要之务便是择定适当的测试模式,依据具体的检测目的与需求,如写入-读出、随机存取等多种测试方式可供选用。其次,测试工具亦是关键要素,市场上众多专业级别的DDR测试工具如SignalTap、HyperLynx等,选择得当将有助于提升测试效率及精确度。

此外,务必关注测试环境的构建与参数设定,以保证测试过程的稳定及可靠性。同样,对DDR测试结果的深度解析亦是关键所在,唯有如此,方能准确探寻问题之根本,并迅速采取有效措施加以解决。

DDR测试中的挑战与解决方案

在实际SOC芯片DDR检测过程中,常面临诸多挑战如时序未聚焦、信号稳定性差等。对此,需采用相应措施确保检测流程流畅进行。

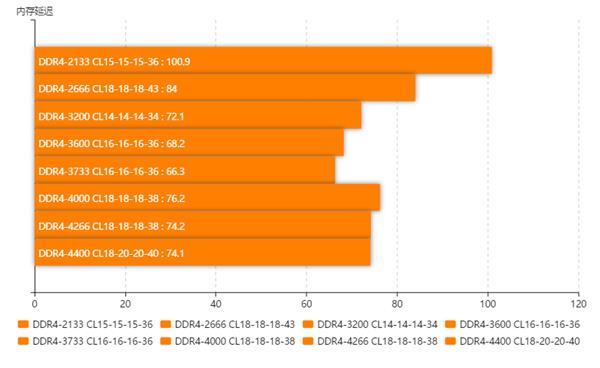

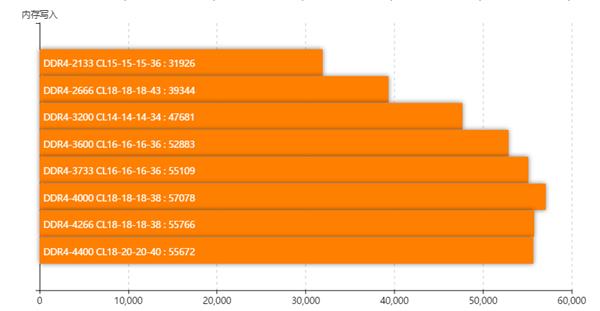

针对时序不稳定问题,可透过调频及调整时序参数等途径优化,保证信号稳定可靠。对于信号完整性的不足方面,可采用布线优化及信号层级区分等技术改良,进而提高信号传输质量。

除此之外,需关注并排除测试过程中误差和干扰因素,以保证测试数据的可靠与准确。

未来发展趋势与展望

随着计算机科技的持续增长与进阶,SOC芯片的DDR测试亦需面对新局势下的挑战及机会。展望未来,随着DDR存储器容量的不断扩展以及速度的逐步提高,SOC芯片的DDR测试亦将趋于复杂且精密化。同时,随着诸如人工智能以及物联网等前沿技术的迅猛崛起及其多元化的应用场景,SOC芯片的应用领域也将日益广阔。

面对未来的发展趋势,我们需不断精进技术实力,探索创新并实现突破,以满足日趋复杂的测试需求及应对挑战。此外,我们也应积极开展跨界合作与交流,携手推动SOC芯片DDR测试技术的发展与进步,为人类社会的智能化进程贡献更多力量。