身为一位资深的计算机硬件工程师,我日常需深度研究众多硬件规范及标准,而DDR4JEDEC时序堪称充满挑战性的课题之一。本文旨在阐述我个人对于该问题的见解与体会,深入剖析其基本原理及其运作机理,期盼能助您拨云见日,揭示此领域的奥秘。

1.DDR4JEDEC时序简介

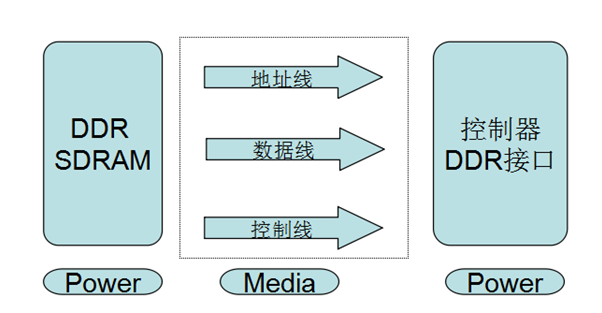

DDR4作为现今主要的内存技术标准之一,其先进之处在于大幅提高了性能与效率以及存储能力。该标准由JEDEC组织精心研发而成,其中时序规则是实现DDR4流畅运转的核心要素。此时序规则囊括了内存访问周期、时脉、延迟时长等关键参数,精准掌握这些时序设定将有助于巩固内存的稳定性及提升性能表现。

DDR4JEDEC时序规范对内存模组及控制器设计产生重大影响,严格遵守此规范保证了系统稳定与卓越性能。在工程实践中,我们需依据该规范设置内存控制器,同时确保内存模块的研发与生产满足其规定,以维持系统的良好运作状态。

2.JEDEC时序参数解析

在JEDEC时序规范中,包括诸多关键参数,皆关乎内存控制器与模块的设计。主要的有:CAS延迟(CL)、RAS至CAS延迟(tRCD)、行地址至列地址延迟(tRAS)及预充电时间(tRP)等。这些参数直接左右了内存模块的读取与写入速度以及稳定程度。

CL延迟即为列地址选通至数据输出间所需时间,是衡量内存读取性能的重要指标。数值越小,读取速率越高,对电压及稳定性则有相应需求。此外,RAS至CAS延迟(tRCD)则代表从行地址选通至列地址选通的间隙时间,对内存写入速度有直接影响。数值小。可提升写入效率,但同时也会加大系统能耗与热量。

3.DDR4JEDEC时序的优化

在实践运用中,为提升系统效能及稳定度,对DDR4JEDEC时序需作出相应调整与优化,主要方法有调整时序参数、加大电源供应、降低时钟频率等。如此恰当的优化措施,既保证了稳定性又可提升内存性能,以满足系统对于内存带宽与延迟的高要求。

硬件设计方面的改进亦可提升DDR4JEDEC时序性能。如依据PCB布局规划提升信号传输效率与降噪;选取优质内存模组及内存控制器芯片以确保系统稳定可靠。这些技术需经工程师在设计阶段细心推敲与实践方能发挥最大效用。

4.JEDEC时序的未来发展

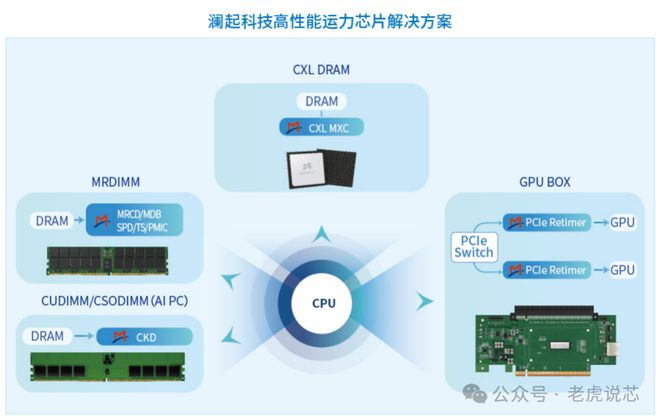

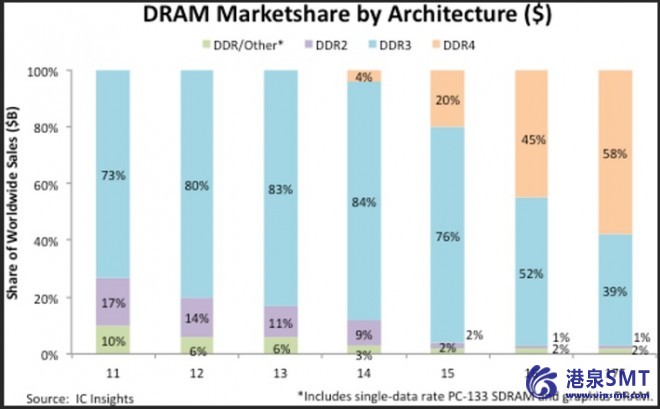

伴随着科技飞速发展及各类应用领域的日益扩大,DDR4JEDEC时序标准亦持续更新与完善。展望未来,我们有望见证更为卓越的时钟频率、微小的时序延迟以及高效节能的特性。另一方面,诸如人工智能、物联网等前沿技术的兴起,必将导致数据处理和存储对内存的需求大幅增长,从而对DDR4JEDEC时序标准带来更大的挑战与期望。

5.内存时序与系统性能的关系

DDR4JEDEC时序对系统性能具有显著影响,有助于改善用户体验。对于性能需求高的应用,如游戏、图像设计等,内存时序优化极为关键。建议通过调节时序参数与优化硬件设计以实现系统性能提升。

6.DDR4JEDEC时序的应用案例

DDR4JEDEC时序被广泛运用到各类计算机系统中,如个人电脑、服务器、工作站等。此时间序的稳定与性能对整个系统的运作有着决定性的影响,因而在设计和调试过程中,工程师会着重考虑其设定及优化,以期保障系统的稳定性与高效率。

7.总结与展望

DDR4JEDEC时序规程,作为内存领域至关重要的参考准则,其对于系统的整体效能与稳健性具有关键影响。因此,对于工程师而言,精通并理解DDR4JEDEC时序规格显得尤为必要。展望行业未来前景,可预见到DDR4JEDEC时序规程将持续改进与升级,以适应日益增长的系统对内存性能及稳定度的需求。

对于笔者而言,DDR4JEDEC时序并非仅仅是技术规范,而是对工程实践与探索精神的体现。通过深度钻研和反复实践,我们得以更好地掌握并运用DDR4JEDEC时序,为系统的稳健运行及性能提高添砖加瓦。