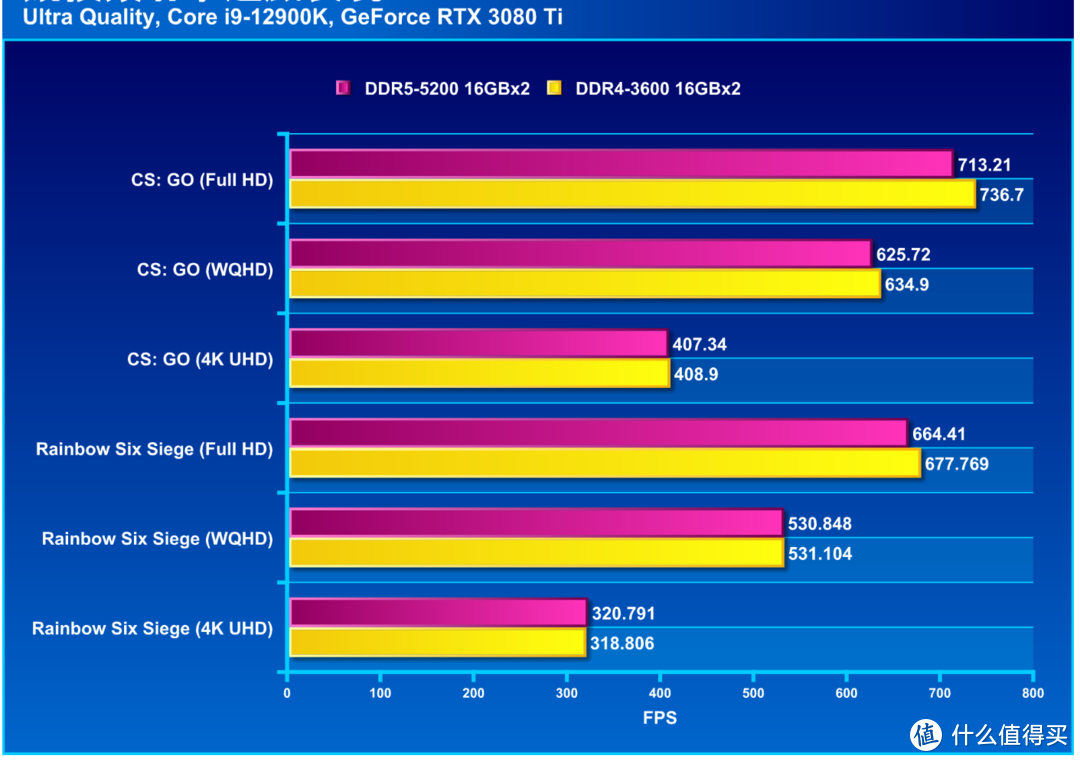

近年科技突飞猛进,电子产品对性能的要求也不断攀升。内存作为计算机硬件核心环节之一,它的效能关乎到整机的运行速率与效果。以DDR5为例,其CL延迟成为业界瞩目的焦点。本篇文章将详细解析DDR5CL延迟的内涵、影响因素及未来走向。

什么是DDR5CL延迟?

DDR5,这一全新世代的双倍数据传输率内存规格,其CL延迟特指CAS延迟,即CASLatency。此参数为内存处理数据的基础时间单位,用以描述从接收到读写请求至开始输出数据所需的时间跨度,常以时钟周期计量。数值愈低,表明内存芯片对读取请求的反应速度更快,性能亦更优越。

DDR5内存CL延迟以整数形式呈现,如CL22、CL18等,数值越小则延迟越短,反应速度越快。然而,此项指标并非仅受内存芯片自身性能所限,还与内存控制器及主板设计等多重因素有关。

影响DDR5CL延迟的因素

内存芯片品质:作为影响DDR5CL延迟的关键因素,高质量内存芯片具备更优的低延迟及稳定性,可适应较高的运行频率。

内存控制器研发:此芯片位于计算机主机板之中,负责高效地协调内存与处理器间的数传运作。优越的内存控制器设计能显著降低数据传输时延,进而提高DDR5内存的性能表现。

主板结构规划与设计:DDR5CL延迟同样受主板构造及布置影响,精细的电路分布、优良的电源供给以及高效的散热设计均有助于提升内存运行的稳定性与性能。

频率及时序调控:DDR5内存的频率及时序设定同样对CL延迟产生影响。适当的频率调节及科学的时序配置可确保内存稳定性的同时降低其延迟时间。

DDR5CL延迟的未来发展趋势

随着科技日新月异和市场态势变化,DDR5CL延迟将有望展现出以下发展方向:

延迟再下探:得益于工艺技术的提升及内存控制器设计的改良,DDR5内存的CL延迟有望再度降低,进一步提高内存响应速度和综合性能。

提升频宽与频率:为应对不断增长的计算需求,未来DDR5内存有望进一步提高其操作频率及带宽。高频宽内存有助于加快数据传输速率,缩短延迟时间。

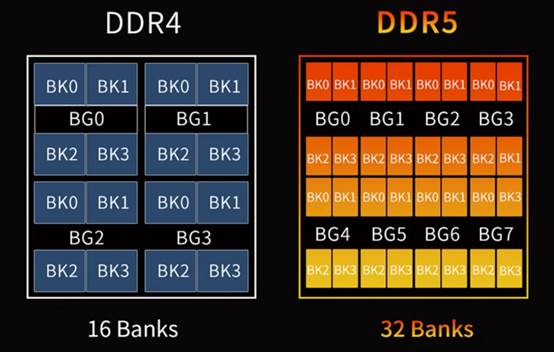

改进架构与协议:DDR5内存架构及通信协议有望进一步精化,从而提高运行效能及稳定性。新型设计可适应多元化计算环境及应用场景。

多通道技术的演进:预见未来DDR5内存将运用更多的多通道技术,通过加大内存信道的数目来提升数据传送速率与内存带宽,从而有效地降低CL延迟。

综合来看,DDR5CL延迟作为衡量内存性能的关键参数,对计算机硬件行业有着极大影响。未来,通过持续改善内存芯片,存储控制器及主板设计等环节,并引入创新性技术与协议,我们有信心实现DDR5内存性能与延迟的双重提升,从而为各类计算机应用提供更为强大的支撑与卓越性能。