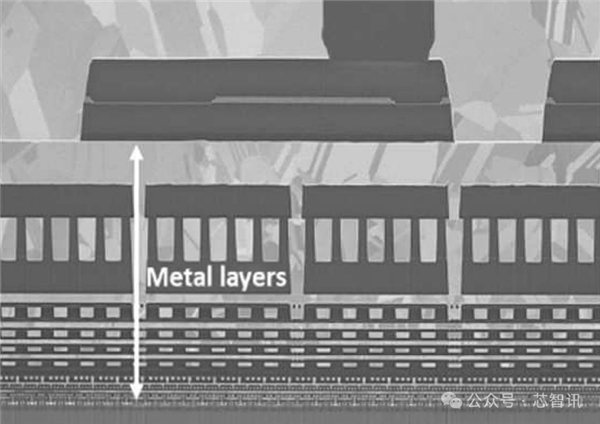

关于DDR4内存,时钟无疑是最关键的组成元素之一。此类存储模块主要由多路时钟信号构成,每个信号在模块操作方面都具有极高的重要性。值得注意的是,DDR4内存内置的时钟数目并非固定不变,而是结合模块本身的特殊设计和需求进行适当调整。在笔者个人看来,此话题颇有研究价值,不妨共同探讨一番。

DDR4内存的基本时钟

首先了解,DDR4内存内含若干种重要的时钟信号,如基础时钟、命令/地址时钟等,这些信号于内存的读写过程至关重要,他们协同处理器数据交换,保证内存正常运转与高效效率。

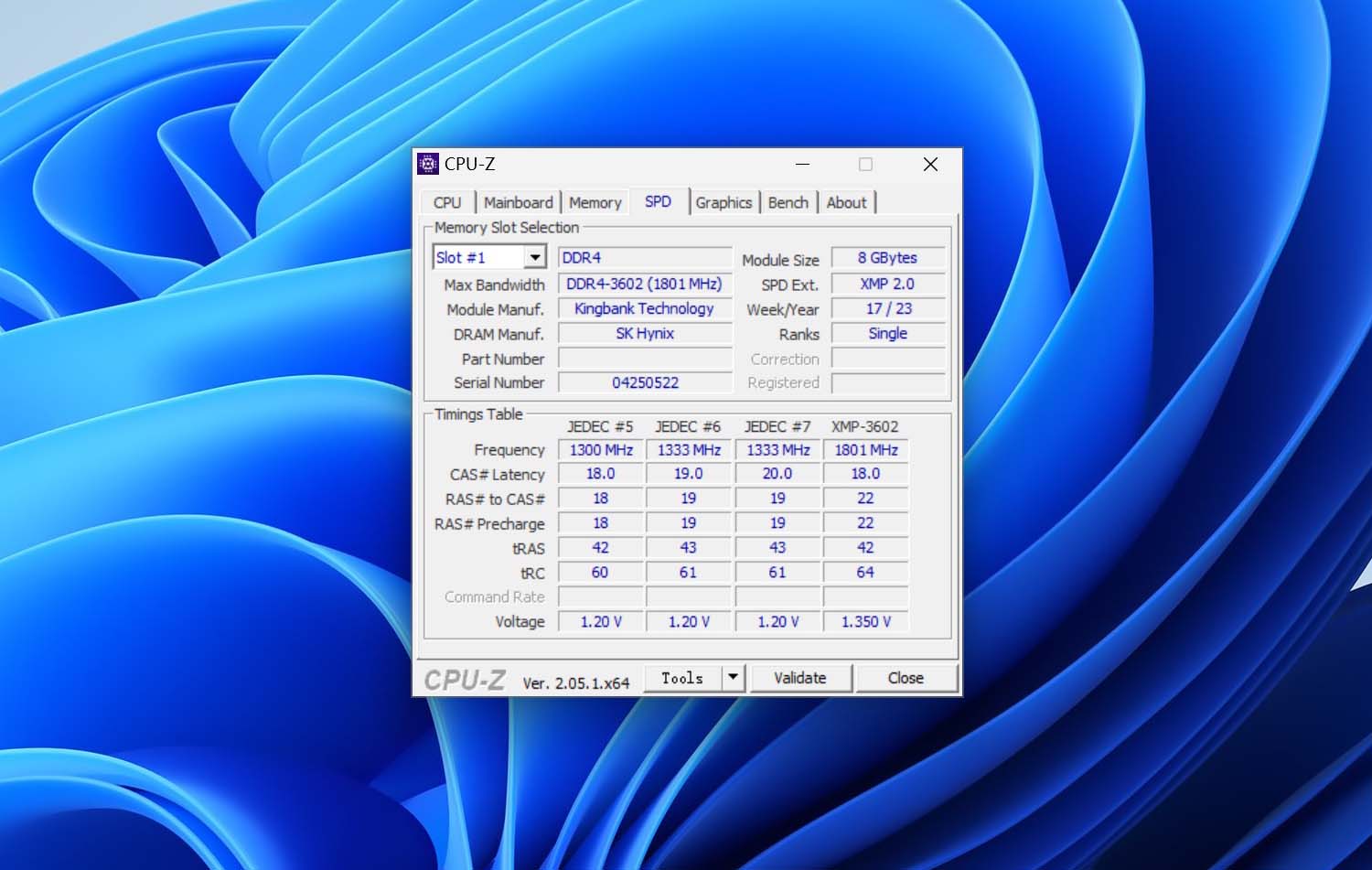

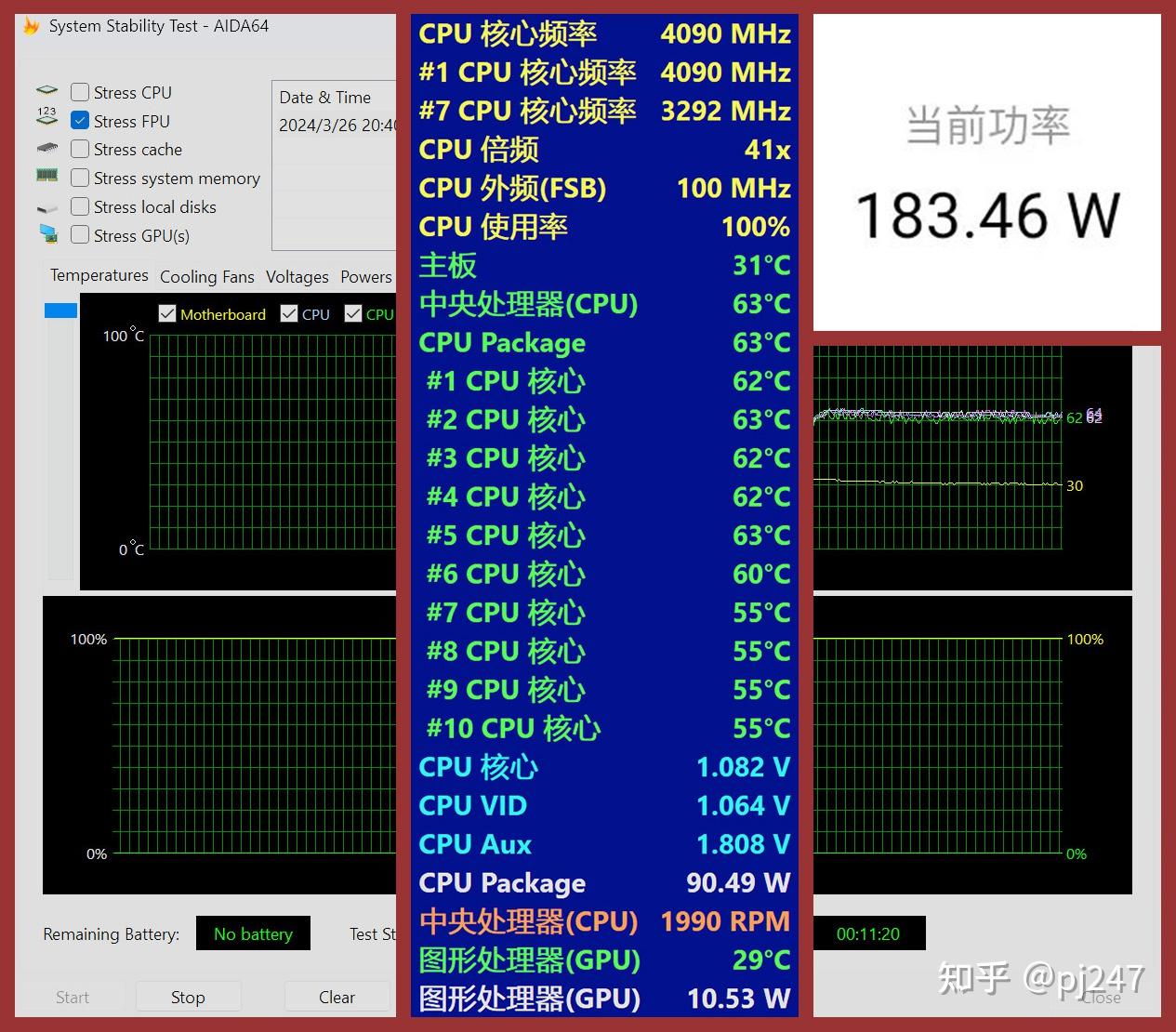

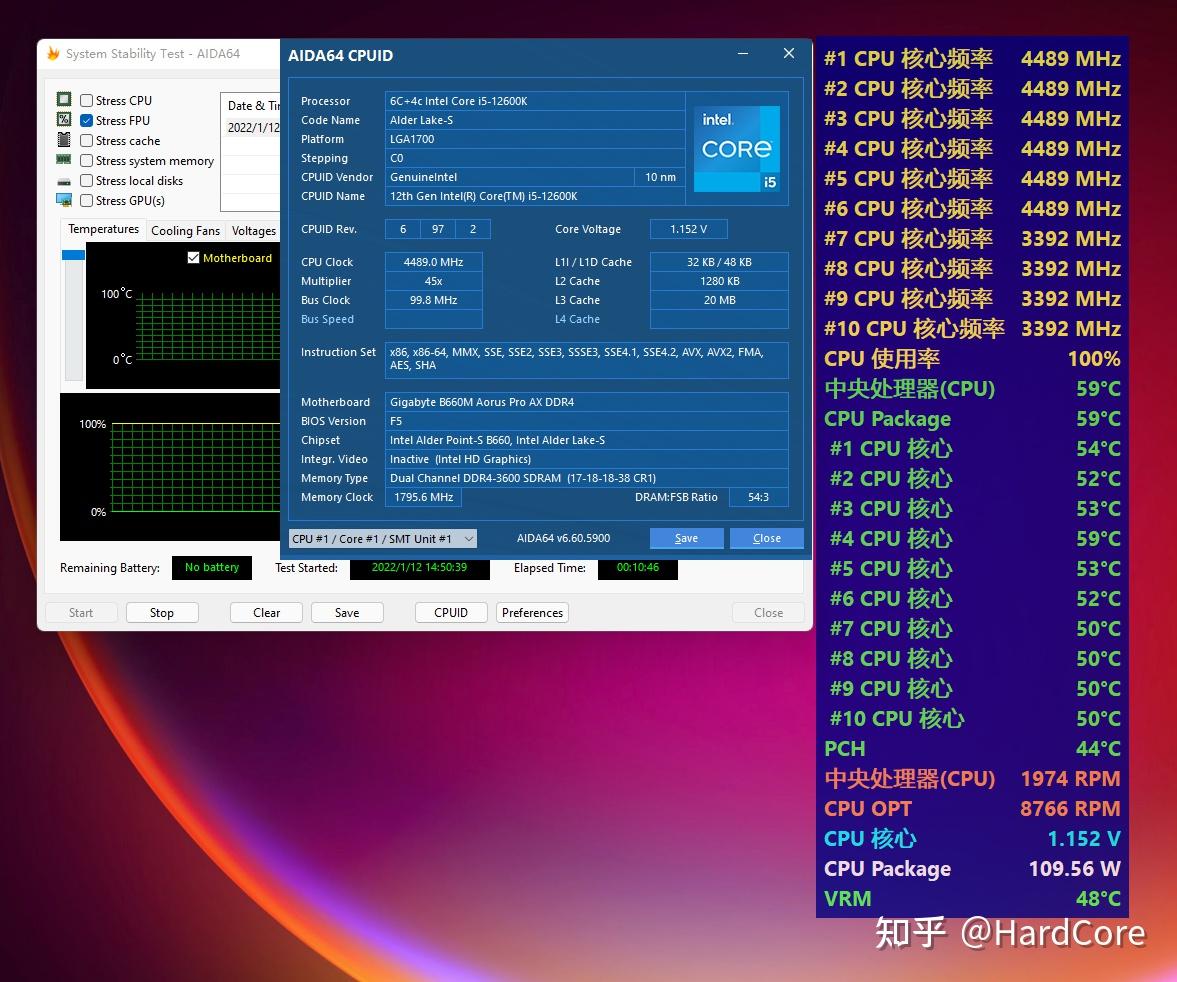

在DDR4内存领域,时钟信号的频率常以MHz计量,因内存模块差异可能有所区别。适当调节时钟频率有助于优化内存性能,然而需兼顾模块稳定性与兼容性。

DDR4内存的额外时钟

除了基础的时钟信号,DDR4存储模块中还有如复位时钟与校准时钟这样的附加时钟信号,其在内存初始化及精准校准阶段具有关键性的功能,能保证存储模块稳定运行于各类环境之中。

由于内存模组个体差异,附加时钟信号的数量与特性会存在区别。如高端DDR4内存模组,可能拥有更为多样且精细的时钟信号布置,进而满足对高性能及稳定运行的需求。

DDR4内存时钟的调节

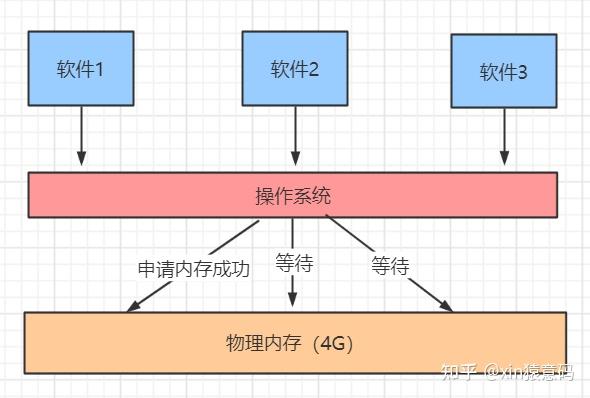

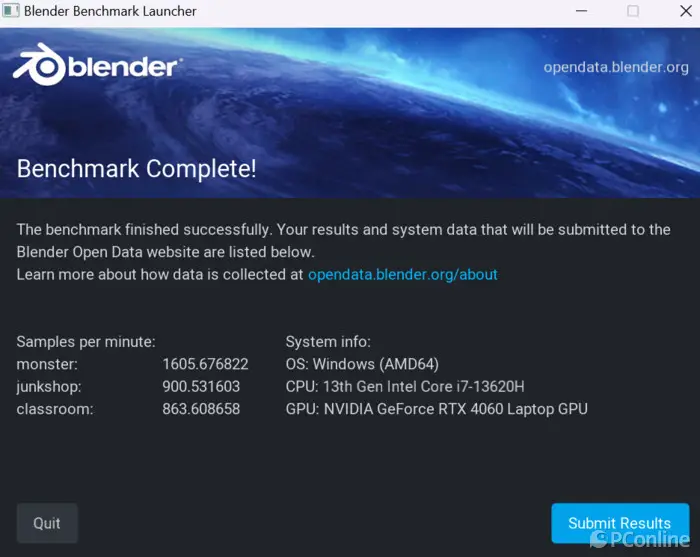

对于广大消费者而言,DDR4内存在大多数情况下是由主板进行自动时序调整,无需用户的干涉。特殊领域如高度技术用户或超频狂热者可在BIOS中自行调整DDR4内存的时钟频率,借此提升运行效率以及系统稳定性。

极具挑战性的是手动调整DDR4存储器高速运行周期,由于专业技术与丰富经验,若是操作不当,将会导致整个系统运行不稳乃至无法开启。因此,请慎之又慎地执行此项任务,以保证系统的稳定性及安全性。

DDR4内存时钟的未来发展

借科技之力,DDR4内存时钟设计日趋精进。展望未来,更智能、效能更佳的DDR4内存设计,将带给用户更卓越的使用感受与性能表现。

同时,新的内存技术如DDR5的崛起,为DDR4时钟设计带来了新的挑战与机遇。未来DDR4内存时钟的演进,引人瞩目,充满无限创新可能。

结语

综观全局,DDR4内存的时钟频率并非固定设定,因内存模组设计及需求而异。时钟在内存中占据举足轻重之地位,因其直接影响到内存性能与稳定表现。对广大消费者而言,熟知DDR4内存时钟设计能助其精确挑选、善用相关存储设备;然而对进阶用户以及超频狂热爱好者来说,深度探索此类知识将有助于实现更为精妙的性能调控与优化。

伴随着科技的飞速发展,我们对DDR4内存时钟技术的智能化与高效性的前景充满信心,其必将提升用户的使用体验。翘首以盼DDR4内存时钟技术的光明未来吧!