身为电子工程专家,我对内存科技充满热忱,尤其关注DDR2内存的内部取样机制。本文旨在解析DDR2内存的内部取样原理,并分享个人学习心得,以期为广大读者揭示其神秘面纱。

DDR2内存的基础知识

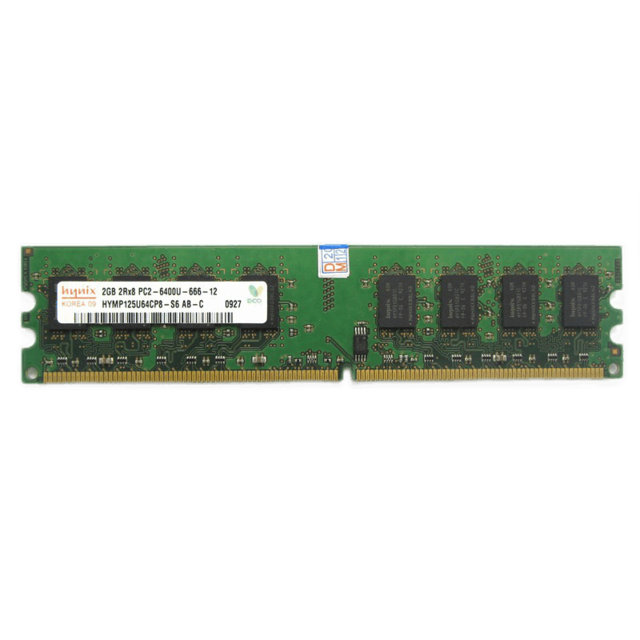

DDR2内存为继DDR后的首款双倍速率同步动态随机存储器(SDRAM),通过提升时钟信号上下沿的数据传输速度,实现比DDR内存翻番的数据读取率。此种内存广泛运用于个人电脑、服务器及其他高性能设备。在深入研究DDR2内部采样机制前,了解其基本结构与特性至关重要。

DDR2内存因其精妙的电路结构和高效的运行频率,在设计与测试环节上需要严格把控精度。关键技术在于其如何在短暂的时间内精准捕获及处理数据。经过深度剖析,我发现DDR2内存的内部采样机制是建立在精密的时序系统之上,该系统涵盖了预充电、行激活、读/写操作以及行关闭等多重步骤。

内部采样原理的深入解析

GDDR2内存的内部分辨原理精确且严谨,需在时钟周期的操控之下高精度读取与写入数据。核心在于实施"双沿采样"技术,即在每一时钟周期的上升沿及下降沿均实现数据传输。此项设计显著提升了数据传输的效率,然而也相应增加了系统复杂度。

为保障数据精确采样,DDR2内存内置精密时序控制机制,确保数据线上的信号于正确时机进行读写操作。同时,为降低信号传输受扰影响,DDR2内嵌有差分信号技术,能对抗环境噪声,提高数据传输稳定性。

信号完整性和时序分析

在DDR2内存运作期间,信号完整性问题不容小觑。数据传输速度极快,任何微小的信号干扰均有可能引发数据传输失误。因此,设计并构建具备良好信号完整性的电路至关重要。借助先进的仿真工具及严谨的测试流程,我们确保了各部分电路在高速运行下的稳定性。

时序分析乃了解DDR2内存采样机制的重要一环,主要涉及合理调整时序参数的设计,以保证数据能按时采集。其中,预充电时间、行激活延迟及读取数据窗口等都需精心计算与设定。精确实施此过程有助于提升DDR2内存效能,预防可能出现的数据误差。

电源管理和能效问题

电源管理作为DDR2内存设计中的关键环节,对提升能效发挥决定性作用。低电压操作模式的引入,有效缩减功耗且延长模块寿命。经过深入探索,我们发现优化电源管理策略可显著降低系统总体能耗。

DDR2内存技术采用了动态电压调整,允许存储模块依据运作负荷高低动态调整供应电压,既保证性能又降低无谓能耗。此电源智能管理模式,对于现今各类电子设备具有关键价值,不仅节约能源,也呼应可持续发展之理念。

故障诊断和性能调优

在实践运用中,DDR2内存常面临诸如数据传送失误、内存耗损等待多种故障困扰。因此,熟练掌握故障检测与排障技艺对保障系统长期稳健运行具有举足轻重的作用。下文将分享如何利用各类专用工具及高效技巧,迅速探寻潜在问题并采用针对性处理策略。

在性能优化方面,我专注于DDR2内存的深度监测与解析,进而准确识别出影响效率的问题所在,然后进行有针对性的改进方案。例如,通过精细调整时序参数或者优化内存布局,我们能够有效提升数据访问速率以及整个系统的运行效能。

未来发展趋势和挑战

尽管DDR2已逐步为更新科技产品所取代,然而在部分关键领域依然具备其独特价值。展望未来,望能见证更多DDR2的优化与突破,尤其是在数据密集型应用方面。

在此期间,我深感探讨DDR2内存取样理论面临诸多挑战,诸如提升数据传输速度、提高内存可靠性以及降低制造成本等方面。然而,我坚信只要持续深入研究与实践,定能攻克难关,推动内存科技的进步。

总结与展望

在深入的学术研究与实际操作中,本人对DDR2内存内部采样机制有了更全面的认识,此番经历既提升了个人的专业素养,也激发了对内存科技发展的热情。期望我的这些探讨与领悟能为广大人群解密DDR2内存的技术脉络提供指导。

末了,我希望提出一问:您对未来内存技术有何见解?面对性能改善与节能之道,如何求得平衡?欢迎在评论区踊跃发表高见,同时请善意点赞并分享此文,推动更多的业内人士参与探讨。