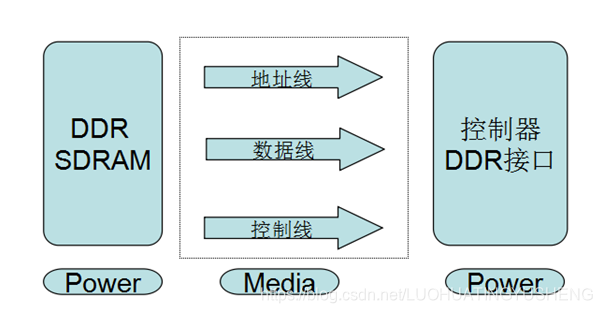

DDR4和DDR3作为内存技术的领军代表,在性能、能耗与布线标准方面各有特色。本文将聚焦布线领域,对这两种技术的细致差异进行深入分析,以帮助读者在工程实践中更深刻地理解其应用。

1.DDR4与DDR3的基本区别

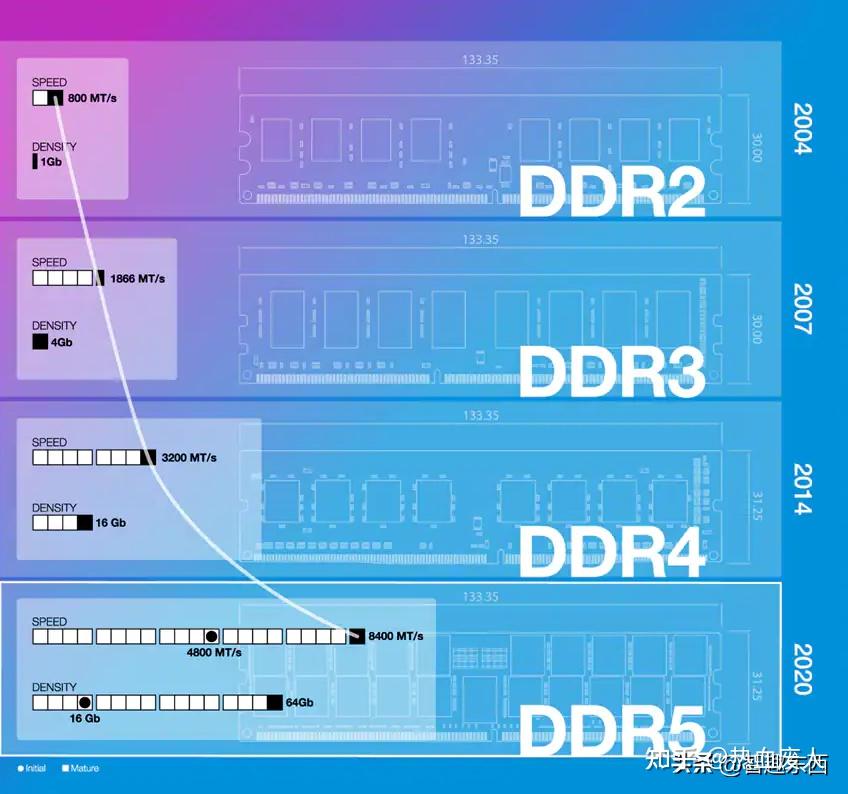

DDR4与DDR3在关键技术参数上有显著区别。DDR4的频率范围为2133MHz至3200MHz,而DDR3则限制在800MHz至1866MHz。较高的频率提供了更迅速的数据传输,但相应提高了布线设计的复杂性。另外,DDR4的供电电压为1.2V,DDR3为1.5V,这使得DDR4在能耗方面更具有竞争力。

在设计中,DDR4对信号完整性设定更为苛刻。随着频率提升,信号沿变得锋利,响应时间加快,布线须细致管理以降低反射和串扰。虽然DDR3布线标准较为宽松,仍须遵从既定准则,以实现信号的稳定传输。

2.布线长度与阻抗匹配

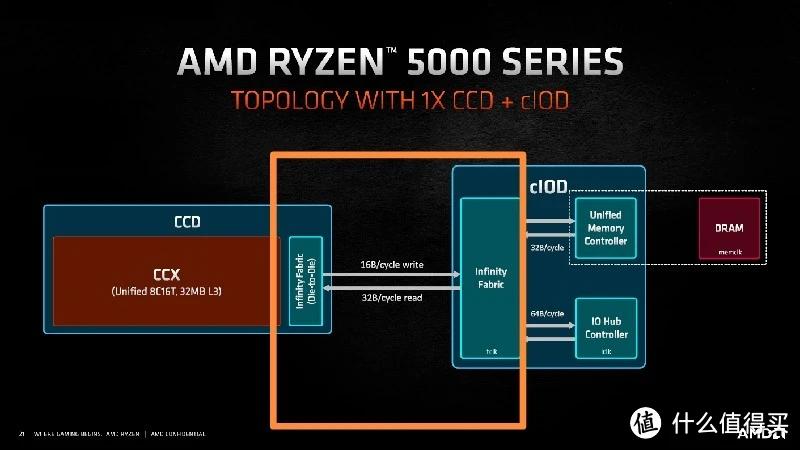

在DDR4线路规划中,确保布线长度均匀至关重要,因DDR4的高频工作特性可能导致信号相位偏移,进而影响数据精确传输。因此,必须在设计初期严格控制布线长度,以达至信号路径长度的一致性。

确保DDR4布线的阻抗适配极关键,需满足信号特性阻抗与终端阻抗的等效,以减少信号反射。根据规范,DDR4的阻抗标准应为50欧姆,故在设计中使用专门的阻抗监控设备至关重要。即便DDR3的匹配要求相对宽松,适当的阻抗管理同样不可或缺,以维护信号质量。

3.电源与地线的设计

DDR4的低电压运行要求电源及地线设计精度提升。在低电压条件下,电源噪声对信号干扰显著增强,从而迫切需要执行噪声抑制措施。常见的方法包括使用多层电路板、增加电源与地线层数,以及于关键信号路径附近部署去耦电容。

在DDR3布线过程中,尽管电源和地线布局同等重要,然而由于电压较高,电源干扰效果有所降低。为确保系统稳定运行,必须对电源和地线进行细致设计,特别是在高密度布局情况中。

4.信号完整性与串扰控制

DDR4的高频性能强调了信号完整性在布线设计中的重要性。缩短的上升与下降时间导致信号边缘速率提升,从而更容易受到串扰影响。为了减轻串扰,DDR4的电路设计中必须实施策略,例如增加信号间距和实施屏蔽技术。

DDR3频率虽不突出,却对信号完整性和串扰要求严格。尤其在布线密集区,减小线间距将增强串扰风险。因此,在设计环节,需作细致的串扰评估,并采取有效措施遏制串扰。

5.时钟信号的布线

DDR4与DDR3的布线结构中,时钟信号处于核心地位。其高频特性要求确保时钟信号的稳定传导。特别是在DDR4的布线设计上,精确的长度和阻抗匹配至关重要,任何偏差都可能导致时钟信号波动,进而影响系统稳定运行。

即便DDR3的时钟速度有限,布线规划必须细致入微。特别是在多时钟域的配置下,确保时钟域间的同步是布线设计中的核心,以避免时钟偏移的发生。

6.测试与验证

完成部署后,DDR4与DDR3的布线稳定性确保需历经严格测试与验证。鉴于DDR4的高频特性,精确测试设备不可或缺,保障信号无损耗与稳定传输。常规测试措施包括眼图分析和时序检验等。

DDR3的测试和验证同等重要。尽管频率较低且对设备要求不高,全面测试仍必不可少,以确保系统稳定和可靠。在量产阶段,测试与验证对保证产品质量极为关键。

7.实际应用中的挑战

在应用实施中,DDR4与DDR3的布线面临多重挑战。尤其是在高密度布线空间受限的情况下,确保固定线长条件下信号完整度成为技术难题。另外,随着技术发展,新型的布线技术及工具层出不穷,将它们高效整合至实际设计中同样是一项重大挑战。

尽管DDR3布线技术已较为成熟,持续优化布线结构至关重要,以满足日益增长的应用需求。特别是在低功耗状态下,如何在保障性能的同时减低能耗,成为研究的关键领域。

在实际设计DDR4与DDR3布线时,需综合考虑频率、阻抗、电源及信号完整性等多重要素,以保证系统性能的稳定与可靠。

结尾问题

在DDR4或DDR3布线阶段,您面临了哪些挑战?如何解决这些难题?敬请于评论区分享您的经验与洞见,以助力我们的学习和交流。