时序余量作为DDR(动态随机存取存储器)领域中的核心概念,直接影响到其性能的稳定性和运行可靠性。该指标具体揭示了在实际操作过程中,时序参数与理论理想值之间所容许的最大偏差幅度。

时序余量概述

时序余量充当了DDR运行过程中的安全防护带。在物理层面上,DDR的信号传输对时序有着严格的规定,数据必须在既定的时钟周期内精确地完成读写等操作。若时序余量不足,哪怕是微小的干扰或频率波动,也可能引发数据读写失误。尤其是在高速数据传输的环境中,时序的微小偏差可能带来灾难性的后果。

此外,时序容限的受限亦由电路布局设计的不当或生产流程的低劣等多重因素所导致,此类问题可能导致时序容限的缩减,进而对DDR的整体性能表现产生负面影响。

时序余量对DDR性能的影响

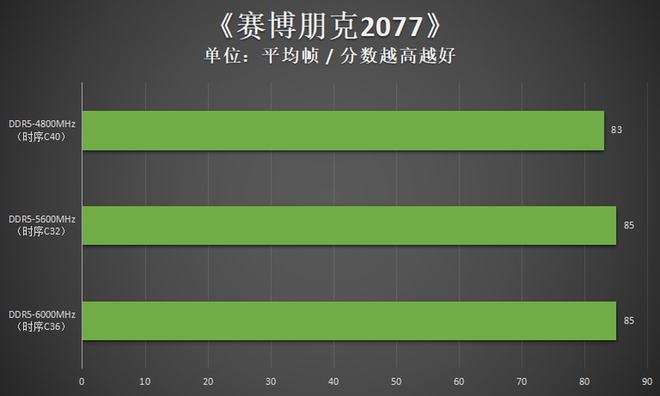

时序余量的充足与否,直接影响着DDR频率的调升潜力。具备充裕时序余量的系统,能够拥有更大的调整余地,以尝试提升DDR的工作频率。然而,若时序余量不足,强行提升频率将可能引发系统不稳定、数据传输错误等一系列问题。以游戏电脑为例,玩家为了提升性能而尝试超频DDR时,时序余量的重要性尤为凸显。

在采用多模块设计的DDR系统架构中,时序容差的变化对内存的兼容性产生显著影响。当不同时序容差级别的DDR模块被混合使用时,由于整体系统时序容差的降低,可能会引发一系列兼容性问题,进而导致系统频繁出现崩溃或文件读写错误等现象。

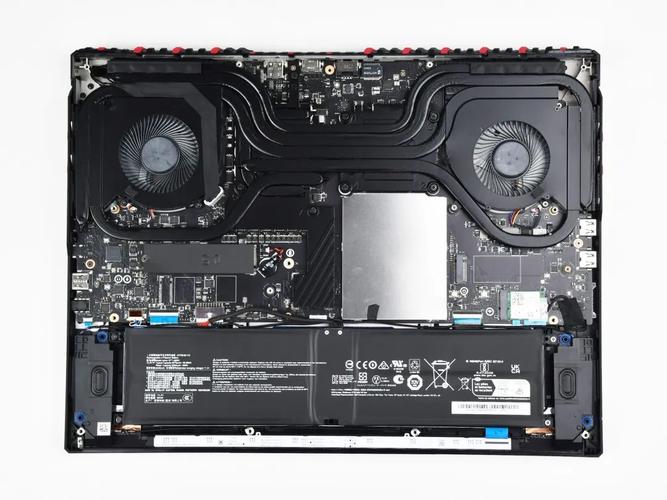

影响时序余量的硬件因素

在PCB电路板设计领域,线路的长度及布局方向等因素对信号传输的延迟起着关键作用。线路过长或布局混乱将直接导致信号传输时间的增加,进而减少时序的余量。这正如一句至理名言所述,绕弯路所耗费的时间必然超过直行,信号传输亦遵循此规律。

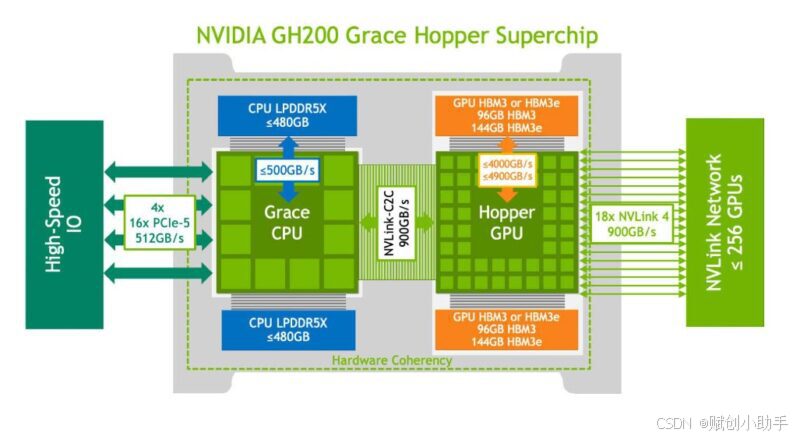

此外,内存控制器亦为关键因素。其性能与设计直接关联至对DDR时序的调控效能。若内存控制器存在缺陷,将难以精确调控时序,进而缩减时序余量。以某些老旧主板为例,其内存控制器可能对新型DDR时序管理存在不足。

在软件层面,BIOS配置扮演着至关重要的角色。在BIOS中,用户能够对DDR的诸多参数进行定制,若这些参数配置失当,将直接对时序余量造成不利影响。以时序参数为例,若调整过小,则会显著缩小时序余量的可用空间。此情形宛如在某一区域中无端缩小了安全界限。

驱动程序同样不容忽视。若驱动程序存在瑕疵或版本过时,其可能无法与DDR设备实现良好匹配,进而引发时序管理上的问题,致使时序余量显著减少。以显卡驱动程序为例,其性能可能对共享显存中DDR的运行时序产生负面影响。

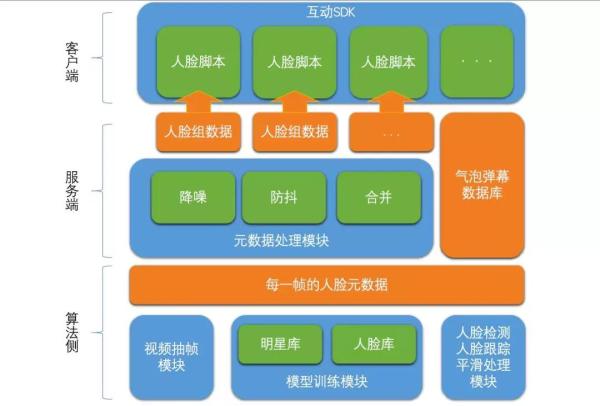

如何测量时序余量

首先,需借助特定的检测工具。市面上存在多种适用于评估DDR时序容差的软件,此类工具能够精确地模仿多样化的操作环境,从而获取精确的容差数据。以MemTest为例,该软件能够在系统运行时对DDR的各项性能指标进行实时监控。

第二点,依赖于硬件测量工具。此类工具能够直接接入DDR电路,从物理角度获取信号传输的时序数据,进而计算出时序的余量。然而,此方法技术要求较高,需具备特定的实验条件,因此普通用户较少采用。

时序余量的优化措施

提升硬件结构设计水平。针对印制电路板(PCB),实施布线优化策略,缩短线路距离以减少信号传输延迟,进而扩充时序容错空间。对企业而言,采纳尖端制造工艺,确保产品品质的统一性。

确保软件配置得当。准确配置BIOS中的DDR相关参数,并定期更新驱动。用户需持续留意厂商发布的BIOS升级提示,一旦发现更新内容包含DDR性能优化,应立即进行升级以增强时序灵活性。

掌握时序余量对DDR系统的顺畅与稳定运行极为关键,您在使用DDR时是否遭遇过由时序余量引发的困扰?期待各位点赞并转发本文,同时热切欢迎大家在评论区发表观点,展开交流。