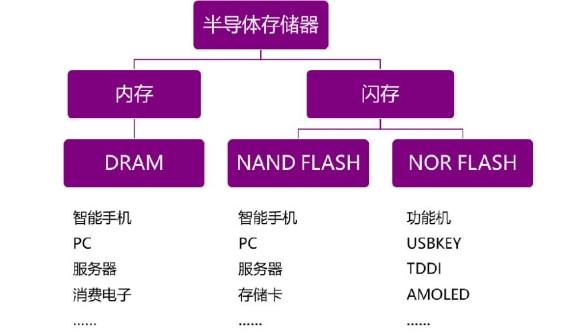

DDRPinDelay对于DDR内存的正常运作至关重要。它指的是DDR电路中,引脚信号传输时出现的延迟。这种延迟会干扰数据的准确传输,并影响DDR模块乃至整个系统的性能稳定。了解DDRPinDelay对于优化DDR电路设计、提升系统整体性能大有裨益。

DDRPinDelay的定义

DDRPinDelay指的是一种电气现象。在DDR电路中,电信号在引脚间传输时,因诸多因素,传输会出现延迟。首先,线路的物理特性,如长度和材质等,会引发信号延迟。线路越长,信号传输所需时间就越长。其次,电路中的电阻、电容等元件也会对信号传输产生影响,改变信号特性,进而造成延迟。在构建DDR系统时,必须考虑到这一点。它直接关系到系统是否能够稳定运行。若忽视PinDelay,可能会导致数据传输错误。

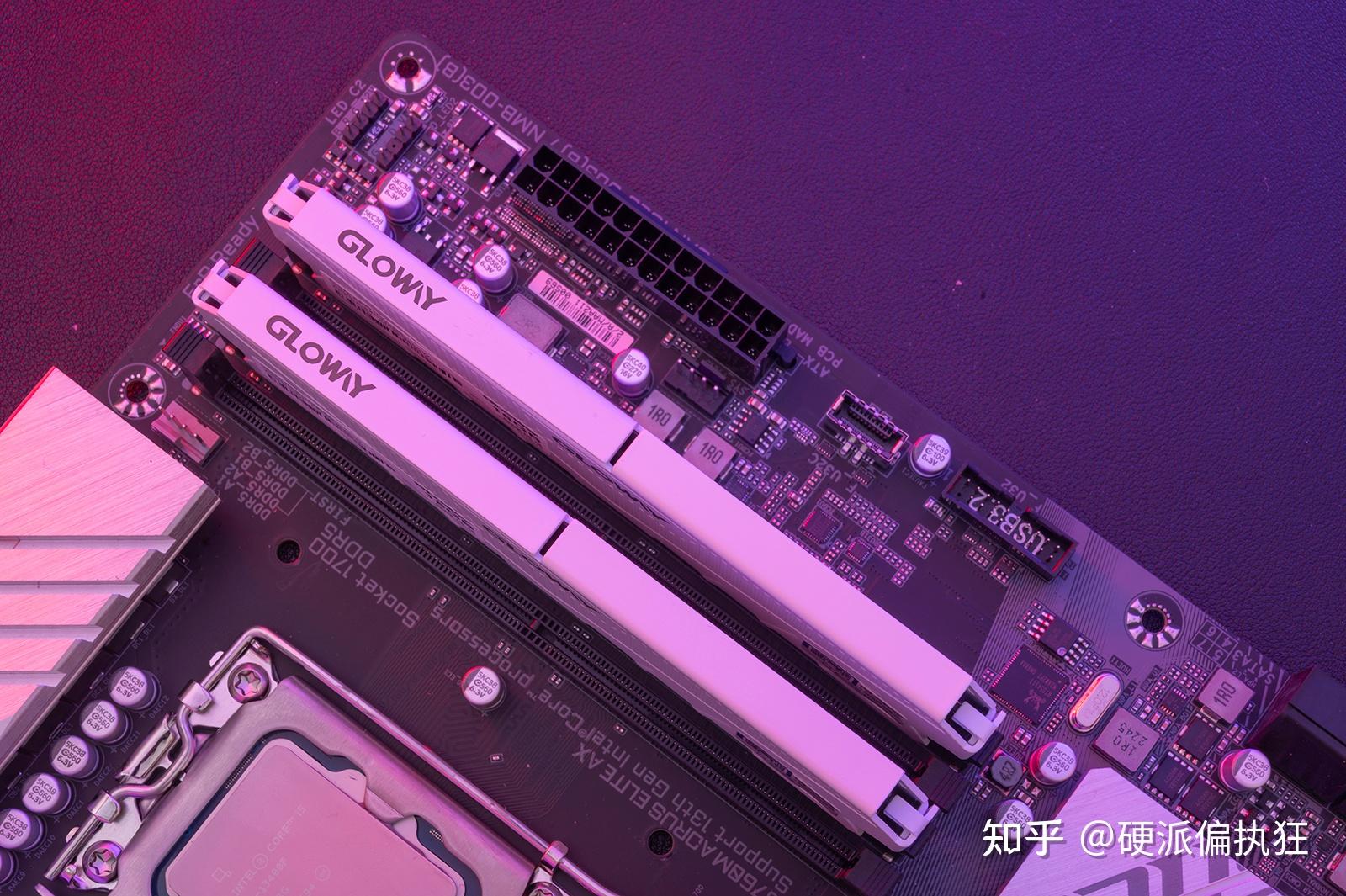

在实际应用中,DDR设备的PinDelay容忍度各不相同。高端DDR模块能较好地应对较大范围的PinDelay,而低廉或低端DDR模块则对PinDelay十分敏感。因此,技术人员在不同应用场景下,需依据所用DDR设备调整电路设计,确保PinDelay在可接受范围内。

导致延迟的因素

线路布局对于DDRPinDelay的影响至关重要。若布局不合理,诸如信号线路过于蜿蜒曲折,或是信号线间距过小导致电磁干扰,那么PinDelay问题便会加剧。比如,在紧凑型电路板设计中,若信号线之间缺乏足够的间隔,电磁干扰便会显著提升信号传输的延迟。此外,线路长度一旦超过设计标准,其物理长度增加也将导致电信号传输时间的延长。

还有一个关键因素是元器件的品质与规格。比如电容的容量、电阻的阻值等,这些都会对PinDelay产生直接影响。若选用的电容或电阻等元器件未能满足DDR电路的标准,就可能引入额外的延迟。这就像在一条本应畅通无阻的道路上,突然出现了不合理的限速标志或障碍物,使得车辆通行速度减缓,电信号传输亦是如此。

对系统性能的影响

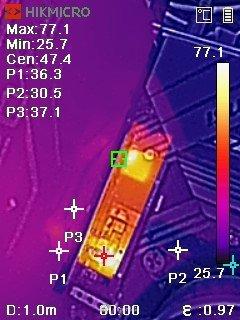

数据传输速度受DDRPinDelay影响,会导致传输率降低。信号延迟使得每个数据单元传输时间延长。以1秒内传输100个数据单元为例,若PinDelay严重,1秒可能只能传输80个或更少。在高速数据传输环境中,这种传输率下降尤为致命。

稳定性方面,它可能引发DDR模块数据错误或不兼容等问题。信号延迟一旦达到一定程度,便会扰乱数据传输的时序,使得接收端无法正确解读数据。比如,在服务器运行过程中,若DDR出现此类不稳定现象,可能引发服务器系统瘫痪或程序崩溃等严重后果。

测量方法

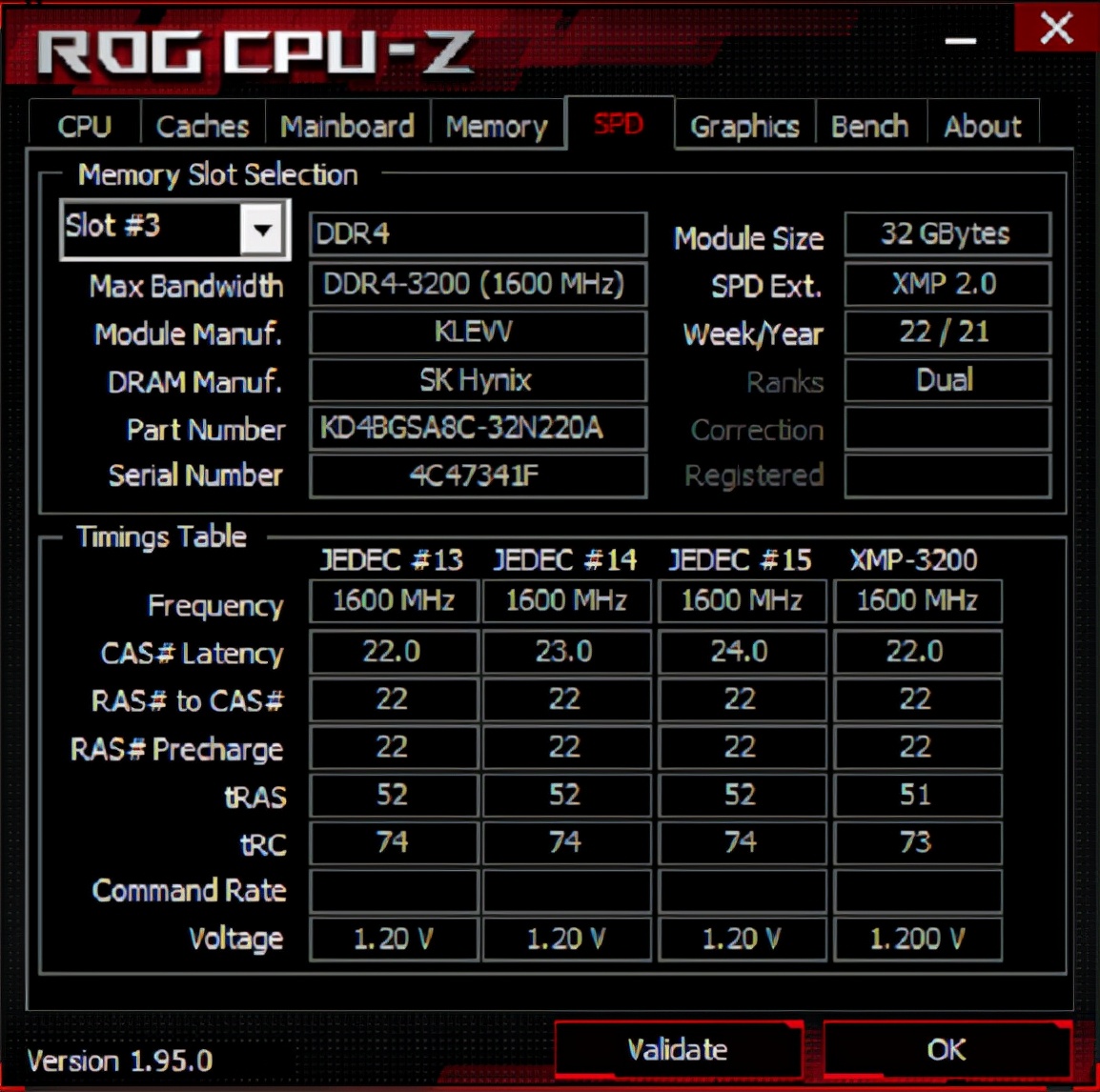

示波器是测量DDR引脚延迟的常用设备。技术人员利用示波器可以捕捉到DDR引脚信号的波形。通过观察波形,可以分析出信号的传输时间和延迟状况。例如,针对特定DDR数据信号引脚,可以在发送端和接收端同时使用示波器进行信号采集。对比两个波形的时间差,可以大致估算出PinDelay的数值范围。

有专门的测试夹具,用于测量PinDelay。它通过特殊电路与DDR电路的引脚相连,能够精确测量信号在引脚间的传输延迟。这种测量方式专业且精准,但操作复杂,对操作人员要求较高,需要掌握一定的电路知识,才能准确使用测试夹具进行PinDelay的测量。

处理措施

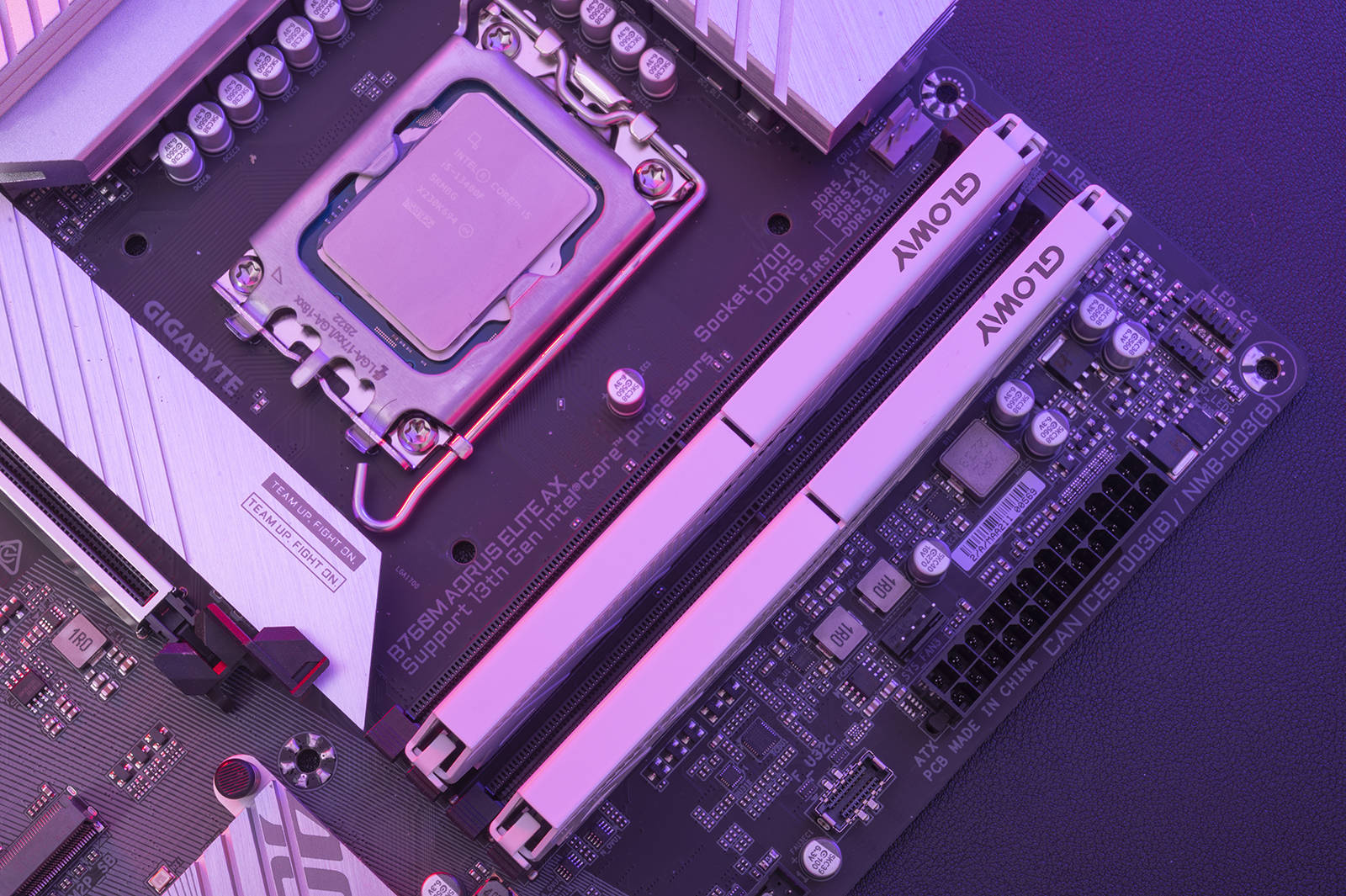

优化线路布局是解决DDR引脚延迟的关键措施。在电路板设计的早期阶段,就要细致规划信号线的路径和布局。应尽量缩短信号线的长度,并确保信号线之间保持适当距离。以设计电脑主板的DDR电路为例,应尽量让信号线保持直线,避免弯曲,以便实现信号的高效传输。通过这种方式,可以显著降低引脚延迟。

调整元器件参数,这同样是一种可行的手段。在DDR电路的实际需求下,需明智地挑选并更换电容、电阻等元器件的参数。若发现是某个电容容量不适宜,导致PinDelay提升,那就应更换为合适的电容。然而,要做到这一点,必须对电路原理有深刻理解,并且具备丰富的实践经验,才能确保参数调整的准确性。

未来研究方向

新材料的研究对DDRPinDelay的优化具有重要意义。若能研制出具备独特电学性能的新材料,并应用于DDR电路的线路生产,有望进一步缩短信号传输的延迟。比如,某些高电导率的复合材料能够使电信号传播速度加快,进而降低PinDelay。

智能算法在DDR电路设计领域的运用或许预示着未来的发展趋势。借助智能算法,我们能够更精确地计算出PinDelay的数值,还能自动优化电路设计。这无疑为DDR电路设计增添了一层智能化的色彩,使得设计和优化过程变得更加高效和准确。那么,大家觉得哪个方向更有望实现重大突破?欢迎读者点赞、分享这篇文章,并积极参与评论。