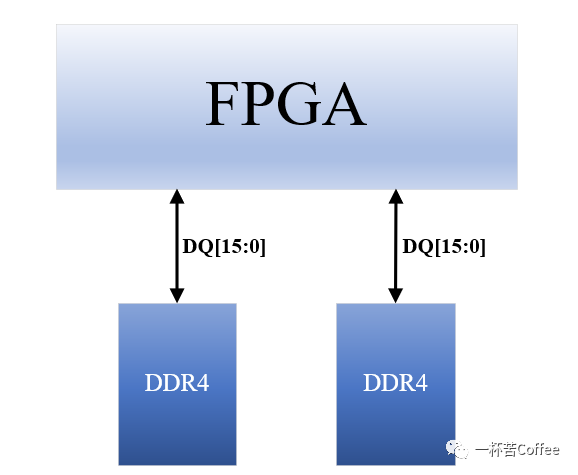

电子电路设计中,绘制DDR线至关重要。DDR线的绘制质量直接影响到内存性能的稳定表现。它对整个电路的可靠运行具有不可忽视的关键作用。这并非仅仅是线路的简单连接,更是一项需要考虑信号完整性、电磁兼容性等多重复杂因素的技术工作。

考虑布局因素

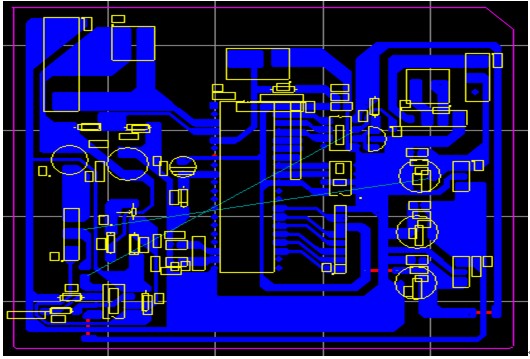

绘制DDR线时,布局至关重要。实际操作中,芯片的不同布局位置对DDR线的影响各异。比如,若靠近电源模块,可能引发电磁干扰,进而影响信号传输的稳定性。因此,DDR线的布局应与关键模块保持适当距离。此外,布局还应考虑布线的复杂性,过于复杂会增加线路间串扰的风险。因此,布局需有全局规划,不能仅关注DDR线本身,而应将其纳入整个电路布局的框架中考虑。

在考虑制作难度时,若布局不当,后续修改将面临诸多难题。若实物制作过程中发现布局问题,返工费用将十分高昂。因此,在设计初期,必须仔细考量布局方案,保证ddr线布局为后续布线和电路整体性能打下坚实基础。这不禁让人思考,在设计电路时,你是否曾在ddr线布局上遭遇过困扰?欢迎留言、点赞和分享你的经验。

信号完整性

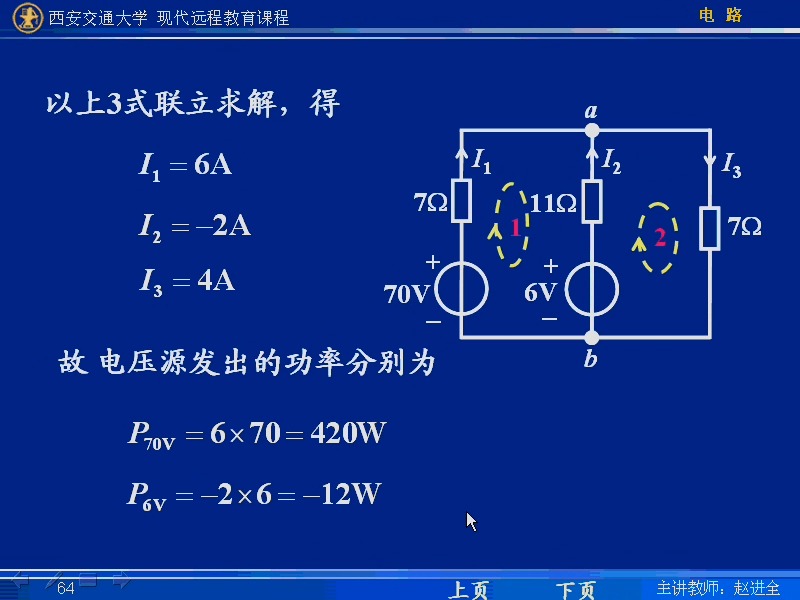

在绘制DDR线路时,信号完整性是一个至关重要的考量点。电信号在传输过程中,很容易受到各种因素的干扰。首先,线路长度的不同会导致信号传输时延不一,若多个信号的传输时延超出规定范围,就可能导致数据读取错误。因此,必须严格限制DDR线路的长度。其次,阻抗不匹配也是一个常见问题,高频信号在传输过程中遇到阻抗变化时,容易产生反射。为此,我们需要合理匹配阻抗,并采用特定的终端电阻等方法,以确保信号质量。

信号线的屏蔽工作至关重要,若未妥善进行,外部电磁干扰便可能轻易侵入信号。尤其是对于ddr这类高速率、低电压的信号,这种干扰更是致命。因此,DDR线周围必须设置有效的屏蔽措施,以确保信号的完整性。那么,各位在处理信号完整性问题时,是否拥有一些独特的小窍门?

电磁兼容性

电磁兼容性,对于ddr线的绘制而言,是一个不可或缺的议题。电子设备的功能越趋复杂,其电磁环境也就越发复杂。ddr线产生的电磁辐射一旦超标,就可能对其他部件造成干扰。在设计过程中,合理调整ddr线的间距,能有效降低线间电磁耦合。而采用差分线设计,则是减少电磁干扰的有效途径,它可以将干扰转化为共模信号,从而降低干扰的影响。

同时,遇到外部强烈的电磁源时,我们必须采取措施来提升ddr线自身的抗干扰能力。这包括增加电磁屏蔽层或优化接地设计。电磁兼容性良好不仅确保ddr线能正常工作,还保障了整个设备的稳定运行。那么,请问在您的设计中,您是如何确保电磁兼容性的?

布线规范

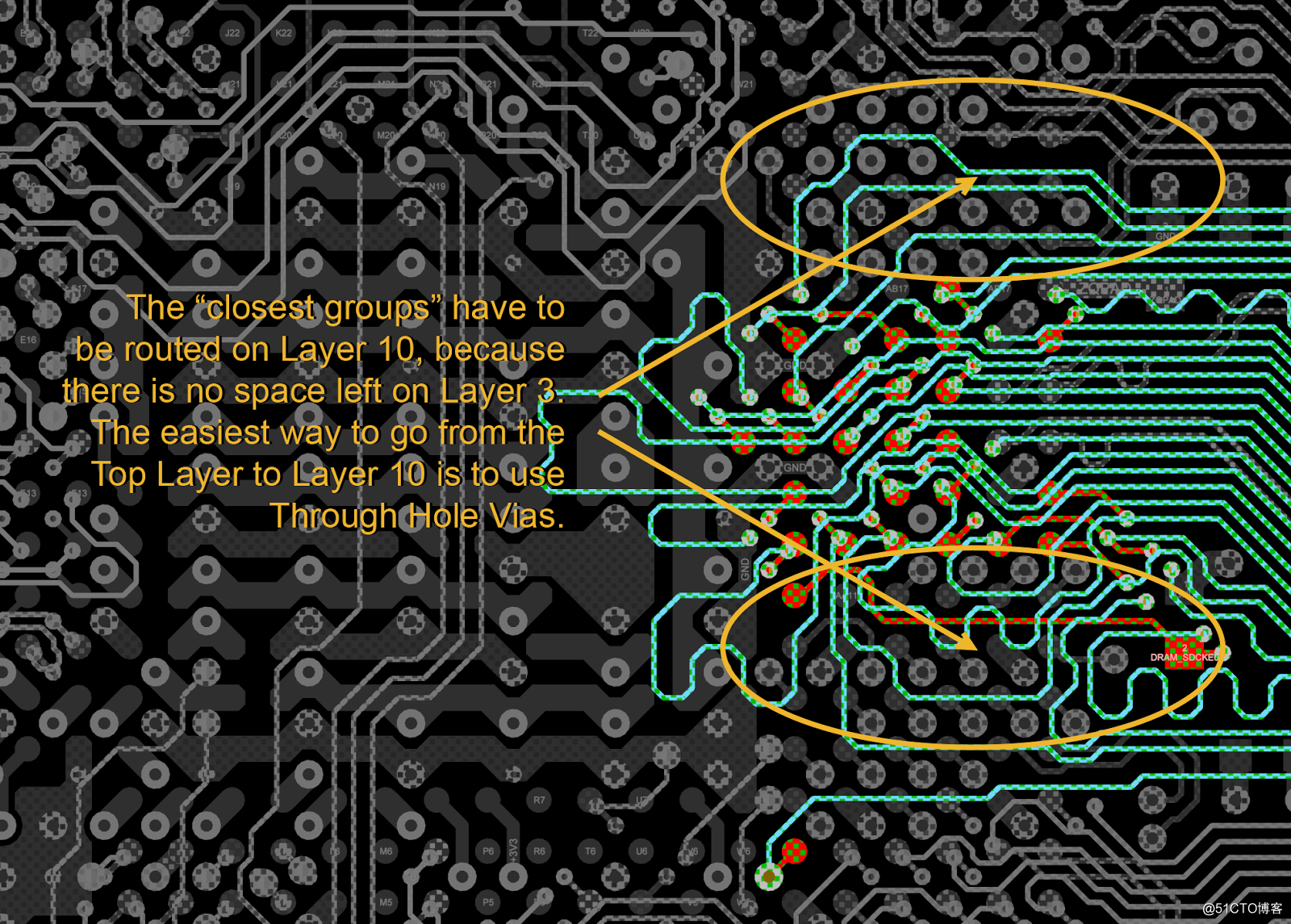

遵守布线规范至关重要。绘制DDR线路时,对线宽和线间距有严格规定。线宽过窄,电流承载能力会不足;线间距过小,容易引起信号干扰。依据行业标准确定合适的线宽和间距,是保证布线质量的基础。此外,DDR线路应尽量直走,减少弯曲。弯曲线路会加剧信号损耗和不确定性。

而且,信号层间的转换必须依照既定规范。若过孔设置不当,信号质量将受影响。例如,过孔的尺寸、形态及数量均可能对DDR线路的信号造成影响。那么,您在遵循这些布线规范时,是始终如一地严格遵守,还是偶尔会有疏漏?

材料选择

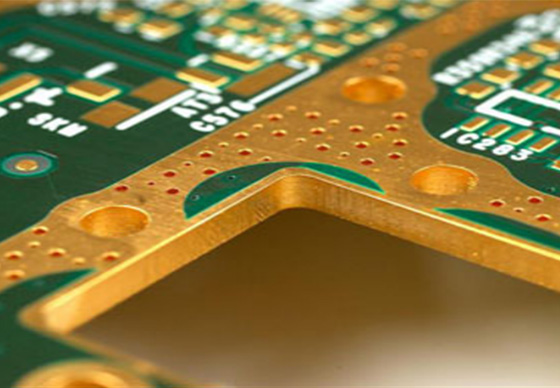

材料的选择对ddr线的性能有着直接的影响。在印制电路板(PCB)的制作过程中,铜箔的厚度和材质对ddr线的电气性能起着关键作用。一般来说,铜箔越厚,其电流承载能力越强,但这同时也意味着制造成本的上升。此外,绝缘材料的选择同样至关重要。使用优质的绝缘材料能够有效降低信号泄漏,增强信号的隔离效果。

考虑到可靠性,我们必须评估材料在各类温度和湿度条件下的表现。比如,某些低档绝缘材料在高温高湿的环境中可能会性能衰减,进而影响信号传输。因此,在挑选材料时,必须全面考虑应用环境,平衡成本与性能。那么,各位在挑选DDR线材时,更看重哪方面的性能表现?

测试与验证

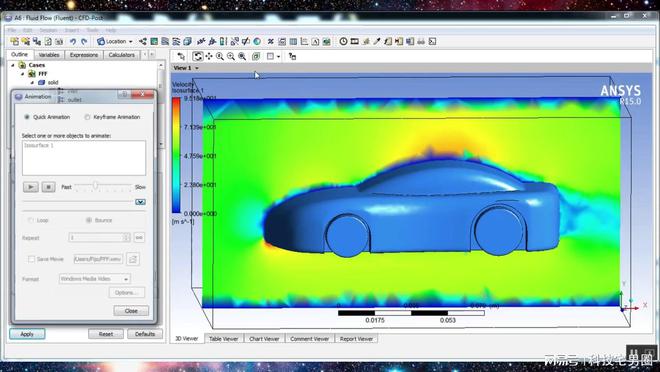

完成绘制并不意味着任务就此结束,测试和验证阶段同样关键。仿真测试能帮助我们提前识别ddr线可能存在的隐患。比如,我们可以使用专业的电路仿真软件来模拟信号传输,检查是否存在信号完整性或电磁兼容性的问题。此外,实物原型制作完成后,实际的物理测量同样不可或缺。

用示波器来观察信号的波形,看它是否符合预期,同时检查信号的电平、上升沿、下降沿等关键指标。如果在测试过程中发现了问题,必须迅速调整设计方案。说到这里,我想问问,你在测试DDR线时,最常遇到的问题是什么?