在数字电路设计领域,Fpga(现场可编程门阵列)与Ddr(双倍数据速率)的搭配应用相当广泛。FpgaDdr的测试环节对于保障系统的整体稳定与可靠至关重要。这一过程涉及诸多专业知识,比如Fpga的配置技巧、Ddr的性能特性以及测试方法等。我们必须持续深入探究,以便更熟练地掌握这两者的结合运用。

Fpga简介

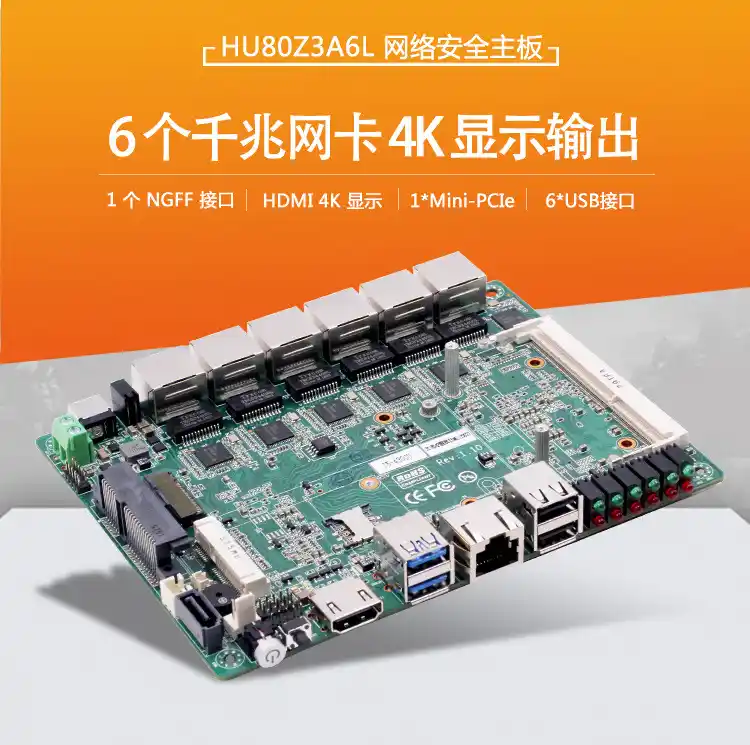

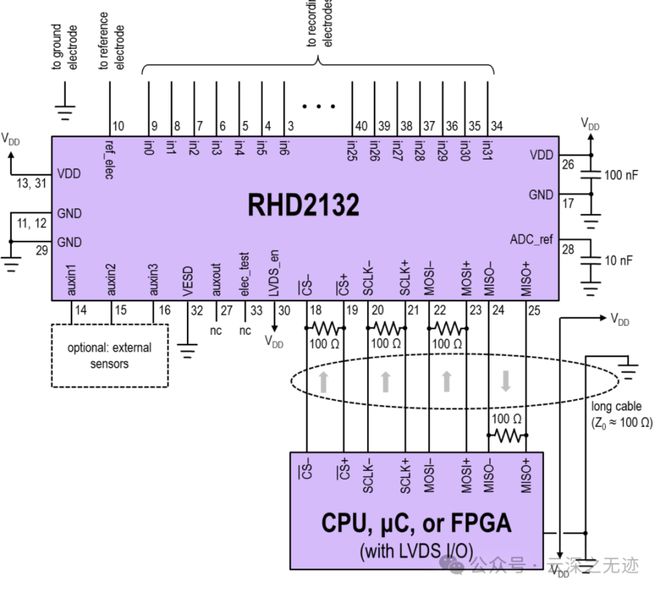

FPGA,即现场可编程门阵列,是一种能够根据用户的具体需求进行编程的集成电路。这种设备具有很高的灵活性,能够针对不同的任务进行定制。它主要由可配置逻辑块、输入输出块以及布线资源等部分构成。在实际应用中,FPGA因其在需要快速和灵活数字逻辑处理场景下的优势,常被选为首选方案,尤其在视频处理等领域。在进行DDR测试之前,我们必须对FPGA有全面了解,因为它构成了整个系统的基石。此外,FPGA还具备强大的并行处理能力,这一点也为DDR数据交互带来了便利。

要明白Fpga的内部构造,对于理解它和Ddr之间的联系至关重要。Fpga内部包含逻辑阵列和寄存器等组件,它们共同协作,处理输入输出的数据。在处理复杂逻辑任务时,Fpga的结构合理性对与Ddr的数据交互效率有着显著影响。

Ddr性能特征

DDR内存的一大特色是它的数据传输速度是普通的两倍。这样的特性使得数据能在时钟的上升沿和下降沿同时传输。在速度上,普通SDR(单倍数据速率)内存根本无法与之相比。DDR的容量也在不断增长,能够满足不断上升的数据存储和传输需求。例如,在高性能计算机系统中,大容量且高速的DDR显得尤为关键。

在实际应用中,Ddr工作时对时序的要求极为严格。稍有差错,便可能引发数据错误或系统崩溃。因此,在测试过程中,对Ddr时序的细致分析显得尤为关键。此外,Ddr的功耗问题同样不容忽视。在功耗受限的情况下,仍能实现高效的数据传输,这正是其卓越性能的体现。

测试目的

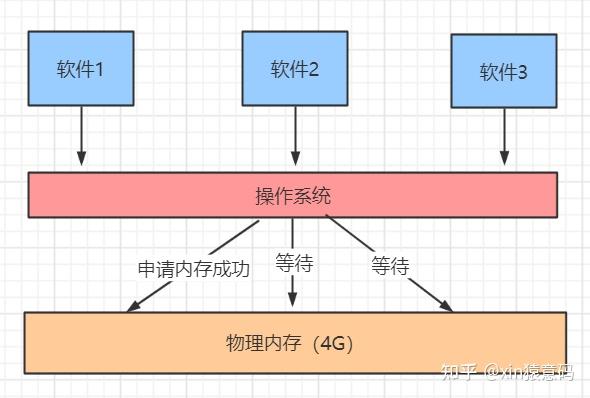

测试的目的是确保Fpga和Ddr能正常运作。首先,必须保证数据传输的精确无误,因为哪怕一个比特的错误,都可能让整个系统无法正常工作。在通信系统中,数据的准确性至关重要,它是系统正常运作的核心。其次,测试还旨在确认Fpga与Ddr之间的兼容性。Fpga的配置必须与Ddr的特性相匹配,这样才能实现高效的数据交换。

新产品开发中,测试不仅在于验证,更在于探寻性能的极致。测试能帮助我们优化Fpga与Ddr的连接,调整相关参数。这就像是在寻找一把钥匙,试图打开一扇通往最稳定、最高效工作模式的大门。

常用测试方法

读写测试是一种常用的检测手段。在这种测试中,Fpga会对Ddr进行数据的写入操作,随后再读取这些数据,以此来比较数据的一致性。这种方式既基础又高效,能够检验数据传输的准确性。在现实应用中,比如服务器数据交互模块的测试,就会采用这种方法。

此外,还有一项重要测试叫做压力测试,这项测试主要是为了检验DDR在高负荷环境下的表现。通过增加数据流量、提升频率等手段,我们可以模拟出极其恶劣的工作环境。机车控制系统中的FPGADDR系统必须经过此类测试,以确保其可靠性,因为机车在运行过程中会遇到各种复杂且恶劣的情况。

测试中的问题处理

测试过程中,数据出错的情况可能发生。这时,必须仔细检查Fpga与Ddr之间的连接线路是否正常,包括物理连接是否松动等问题。就好比汽车油路断了,无法正常行驶,线路一旦出现问题,数据传输也将无法正常进行。同时,还需核实两者的配置参数是否准确无误。

时序问题常常会出现。一旦遇到时序问题,我们得从时钟信号的产生和分配开始着手。这时,借助专业的时序分析工具,比如ModelSim,进行深入的分析和排查是很有帮助的。这就像侦探在案发现场寻找线索,不能遗漏任何细节,才能准确找到问题所在并加以解决。

未来展望

技术不断进步,Fpga与Ddr的性能将不断提升。展望未来,我们或许会见到速度更快、功耗更低的Ddr。这样的变化无疑会给测试技术带来新的挑战。同时,新型Fpga架构也将问世。那么,如何将这些新型架构与现有技术有效结合,实现高效准确的测试,便成为了一个值得深入探讨的问题。

复杂的应用场景往往促使产生更多独特的测试要求。以物联网设备为例,在设备体积和能耗的严格约束下,FpgaDdr的测试又该如何作出调整?在此,我想请大家思考一个问题:你们认为,在未来的FpgaDdr测试中,我们最需要解决的难题是什么?欢迎大家在评论区积极留言、点赞并分享这篇文章。