DDR的复位时间是其正常运作的关键指标之一。在众多电子设备中,DDR扮演着至关重要的角色。其复位时间的长短直接影响到它是否能够稳定运行,以及整个系统是否能够准确无误地工作。这种设置的确定并非随意,而是需要全面考虑各种因素。

复位的基本概念

DDR的复位行为实际上是一个初始化的过程。这种良好的复位能让DDR从已知初始状态开始运作。就好比启动一台复杂的机器,得先进行基础设置和复位。在硬件层面,复位信号会设定一些内部寄存器的值,以规范后续的读写操作。通常,复位时间过短会导致某些内部逻辑未能正确初始化。比如,某些配置寄存器的值可能还没被设置为预期的初始值,这可能导致DDR操作中出现不可预期的错误。

从逻辑层面分析,若复位时间未达标准,DDR各逻辑模块间的协作将遭遇挑战。举例来说,数据选通逻辑、地址映射逻辑等均将受影响,这好比一支队伍未充分了解各自职责便开始行动,混乱在所难免。因此,复位时间对DDR稳定运行至关重要,是保障其顺畅运作的基石。

与硬件电路的关联

DDR的复位时间必须与连接的硬件电路相匹配。不同的硬件电路各具特点。若DDR的复位时间与主板电路设计不吻合,情况严重时,可能会导致硬件损坏。在设计主板电路时,往往会对DDR的复位提出特定要求。例如,对于高速运行的主板电路,它们可能需要DDR的复位时间更加精确,以便适应快速的数据传输需求。

硬件电路的供电稳定性对DDR的复位时长需求有影响。供电不稳定时,可能需要适当增加复位时长,以确保DDR内部状态能正确初始化。不稳定供电可能导致电路模块工作延迟,若复位时长不足,就无法满足所有模块的初始化需求。这就像在糟糕的路况下开车,需要更长的准备时间才能启动。

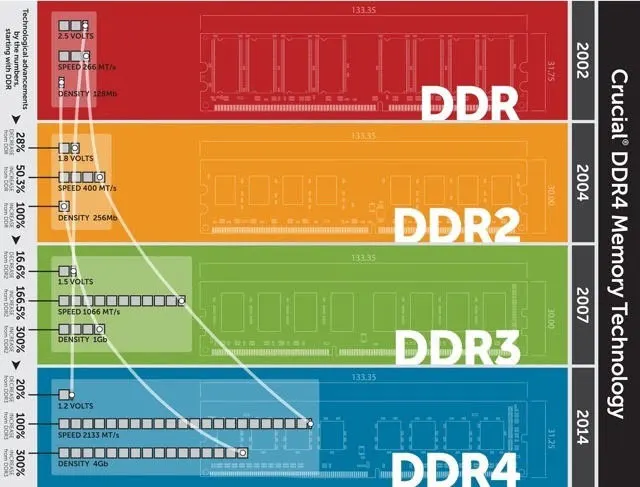

不同DDR类型的差别

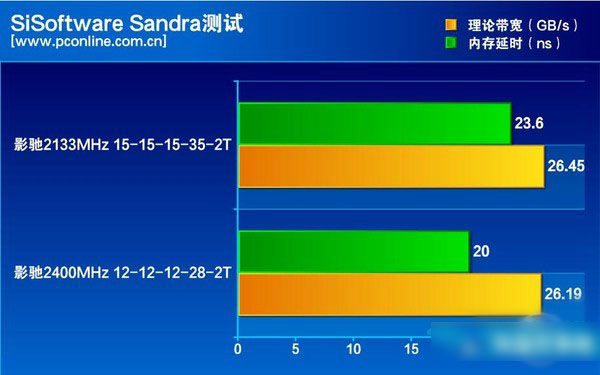

DDR有多种类型,比如DDR3和DDR4等,它们对复位时长的需求各不相同。DDR4相较于DDR3,内部结构更为复杂,传输数据速度也更快,因此对复位时长的控制要求更为严格。DDR3可能在较短的复位时长内就能进入初始稳定状态。

DDR4技术升级后,复杂度提高,若复位时间设置不当,会影响其多存储块同时工作的性能。相较之下,DDR3的操作较为简单。为不同DDR类型设定恰当的复位时长,是确保系统内存高效稳定运行的关键。混淆DDR类型,可能导致复位时长设置出现较大误差。

时钟信号的影响

在DDR的工作流程中,时钟信号扮演着指挥棒的角色。这一信号对DDR的复位时间长短起着至关重要的作用。一旦时钟信号出现不稳定或频率不匹配,便直接干扰了复位时间的准确性。在高频时钟信号的驱动下,DDR内部的逻辑切换速度加快,这时对复位时间的精确度要求更高。

从同步的角度来看,时钟信号的运作必须与DDR的复位同步。一旦时钟信号与复位时长不匹配,数据读取和写入可能会在错误的时间发生。打个比方,就像乐队演奏,每种乐器都得跟着指挥的节奏来演奏。要是指挥的节奏(时钟信号)和乐器的准备时间(复位时长)不协调,整个演奏(DDR工作)就会变得混乱不堪。

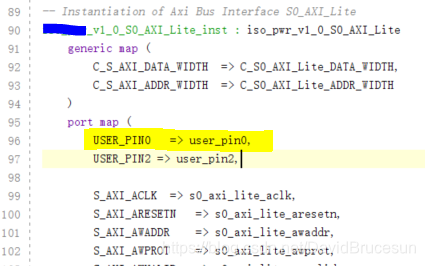

软件配置与复位时长

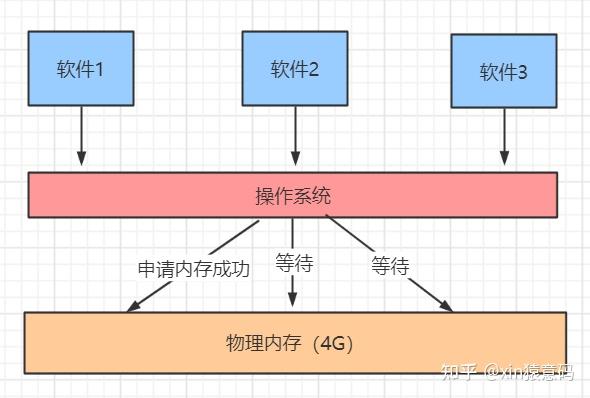

软件层面上,我们可以对DDR的复位时间进行配置与调整。在BIOS(基本输入输出系统)中,部分设置与DDR的复位时间息息相关。有些BIOS版本内置了预设的DDR复位时间,但这些预设值并不总是适用于所有情况。

对于高级用户或系统开发者而言,手动修改BIOS的相关设置变得极为关键。不当的软件配置可能导致DDR复位时间超出合理区间。比如,若软件中设定的复位时间远短于实际需求,便可能引发硬件层面复位时间不足的问题,进而造成内存分配混乱等状况。

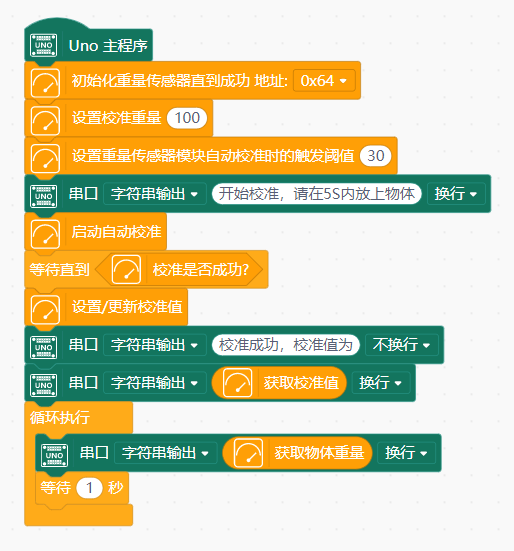

测试与优化策略

产品设计和开发阶段,对DDR复位时间的检测至关重要。借助专业的测试设备,我们能够精确测量复位时间,同时识别出潜在的问题。例如,示波器这类测试工具能直观展示复位信号的持续时间及波形特征。

优化DDR的复位时长是一项持续的优化工作。我们需要不断调整硬件电路的参数和软件的设置,以实现复位时长的最佳状态。这样做不仅能够确保DDR的稳定运行,还能提升整个系统的性能。若对复位时长不加以控制,系统可能会陷入不稳定的状态。

我想请教各位一个问题:在使用电子设备时,你们是否遇到过因为内存问题导致设备出现故障的情况?期待大家的评论参与、点赞以及文章的分享。