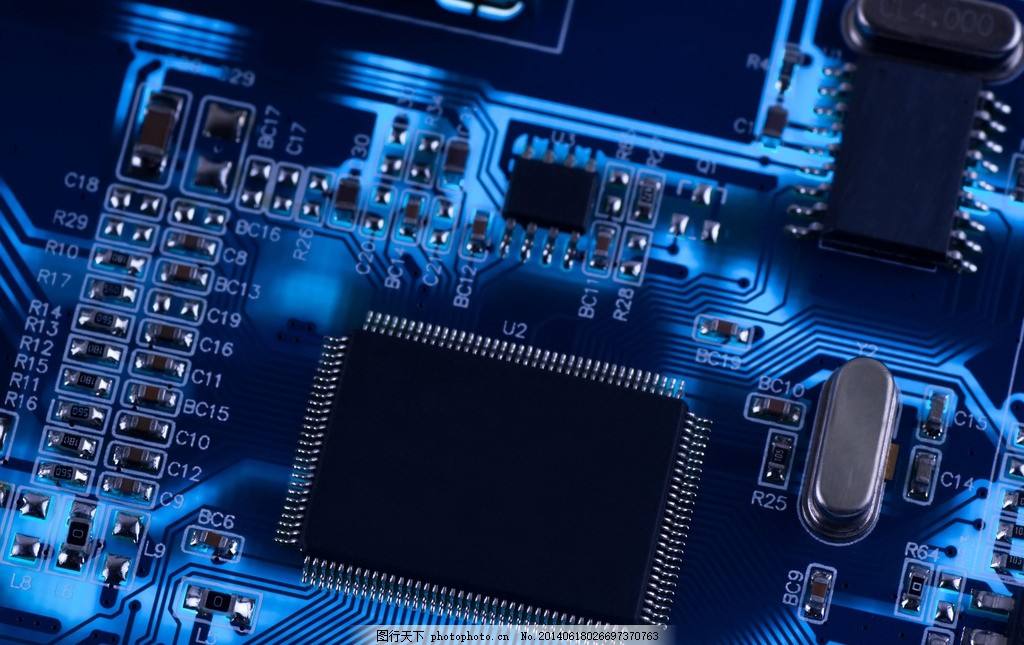

在电子电路设计中,DDR单线阻抗占据着至关重要的地位。它直接影响到信号传输的完整性和稳定性。不同DDR系统,甚至是同一系统中的不同线路,对单线阻抗的要求和影响因素都十分复杂多样。理解DDR单线阻抗,就如同破解电路之谜,对提升整个DDR系统的性能至关重要。

定义与概念

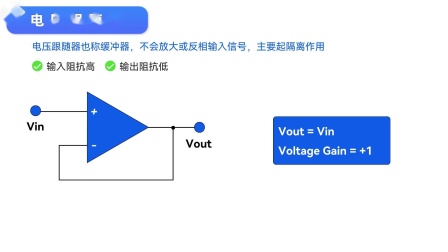

DDR单线阻抗究竟是什么?简而言之,它指的是在DDR信号传输过程中,电流所遭遇的阻力大小。这种阻力大小是由多个物理特性共同决定的,比如线宽、线长、介质材料等。从物理学的角度来看,它遵循一定的电学原则。例如,根据欧姆定律,通过调整线的电阻等参数,我们可以改变单线阻抗。在实际应用中,它表现为信号在传输过程中所遇到的阻碍。了解这些基本概念,是深入理解DDR单线阻抗的关键。

DDR单线阻抗的标准定义遵循一定的规范。在国际标准组织里,对它有详尽的定义和测试方法的规定。电子设备制造商必须遵循这些规定,以确保不同设备间DDR信号的正常交流。DDR的每一代都有其单线阻抗的标准,这些标准随代数不同而有所变化。要准确掌握特定DDR类型的单线阻抗特性,就必须了解这一变化规律。

影响因素

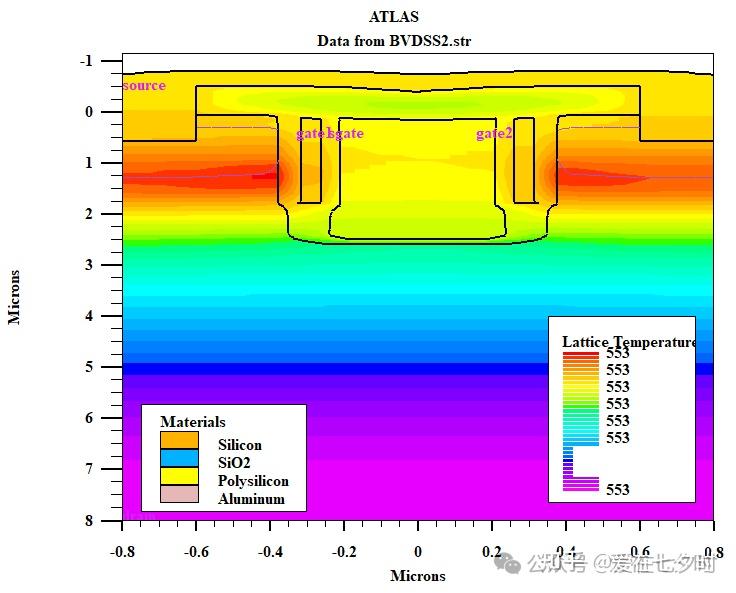

布线结构对DDR单线阻抗的影响显著。以微带线和带状线为例,这两种常见的布线结构。微带线一面接地,一面是空气,其特性使得与带状线相比,单线阻抗值存在较大差异。在设计时,若选用微带线,必须精确调整线宽,以适应DDR信号传输,因为线宽的微小变化都可能使单线阻抗超出合理范围。

线路材料的挑选对于DDR单线阻抗的影响同样不容忽视。各种电介质材料因其介电常数各异,这会进而影响到电场的分布,从而改变单线阻抗。以常用的FR4材料及一些新兴的高频材料为例,选择时必须考虑实际需求与DDR的特性。一旦选材不当,不仅DDR单线阻抗会不匹配引发信号问题,还可能引发成本浪费等一系列不良后果。

测量方法

时域反射计,简称TDR,是测量DDR单线阻抗的常用工具。它通过发送脉冲信号沿传输线传播,当信号遇到阻抗不连续点时,部分信号会反射。通过测量反射信号和入射信号的幅度和时间等参数,可以精确计算出单线阻抗值。此外,这种方法还能精确定位信号质量问题的具体位置,便于调试和改进。

网络分析仪也可用于测量DDR单线的阻抗。它能测定不同频率下的S参数,并据此解析出传输线的单线阻抗。尤其在测量DDR单线的高频段阻抗时,此方法显得尤为有效。它能绘制出详尽的频率响应图表,为DDR系统的整体优化提供了详实的数据支持。

重要性体现

DDR单线阻抗对数据传输的精确度有重要影响。若DDR单线阻抗不匹配,信号在传输过程中容易产生失真。这就像声音在遇到障碍物干扰时会发生变化,DDR信号亦是如此。在众多对精度要求极高的电子设备中,比如高端服务器,对DDR单线阻抗进行精确控制,就能确保数据传输存储毫无误差,实现快速无误的数据传输。

这同样关乎DDR系统的稳定性。单线阻抗的不平衡会引发信号反射和串扰等问题,进而干扰DDR模块的读写操作。在工业控制设备中,若DDR系统因单线阻抗问题而不稳定,可能会引发生产错误等严重后果。

优化策略

在PCB的布局布线阶段,合理规划是提升DDR单线阻抗的关键。工程师需通过调整线宽、间距和布线层等方法,使单线阻抗接近理想值。为此,设计阶段就要制定详细准确的布局布线方案,并根据实际生产工艺进行调整。

匹配网络的设计对DDR单线阻抗的优化起到了显著作用。它能有效降低信号反射。依据线路的具体特性,设计出恰当的匹配网络,如终端匹配等方法,能让DDR信号在传输过程中更加顺畅。这种做法对于提高DDR系统整体性能而言,是不可或缺的重要手段。

常见问题及解决

常见的问题之一是,实际测量的DDR单线阻抗与设计数值存在差异。在这种情况下,首要任务是检查布线是否与设计要求有所偏差。或许,在PCB板实际制作过程中,微小的误差导致了线宽或线间距的改变,进而影响了阻抗。这时,就需要重新制作或进行电路的补偿性调整。

此外,还有一个问题是不同DDR模块间的连线单线阻抗不一致。这时,我们可以通过在连接线路中添加调节电路或使用特殊的连接线材来实现阻抗统一。关于这个问题,我想请教各位读者,在解决DDR连线问题时,你们是否遇到过其他难题?同时,也欢迎您点赞、分享这篇文章,让更多人从中受益。