当前,随着科技的迅猛进步,半导体技术的创新成为业界关注的中心议题。据快科技12月8日的报道,在即将到来的IEDM2024会议上,英特尔展示了其四大半导体制造工艺的突破,这些进展引发了业界的广泛关注。

四年五个工艺节点计划

Intel正全力推进其涵盖四年、五个工艺节点的战略规划。到2030年,其目标是单个芯片集成1万亿晶体管。这一目标既宏大,也反映了当前科技发展的水平。这表明Intel对未来几年在晶体制程领域抱有高期望。同时,这也反映了科技界对晶体管、缩微、互连和封装技术的重视,这些技术是实现该目标的核心。实现这一计划需投入大量研究资金,Intel能否成功实现目标,备受关注。

该计划展现了Intel在半导体行业的远大抱负。Intel正致力于追求更尖端的技术,以此增强其市场竞争力。

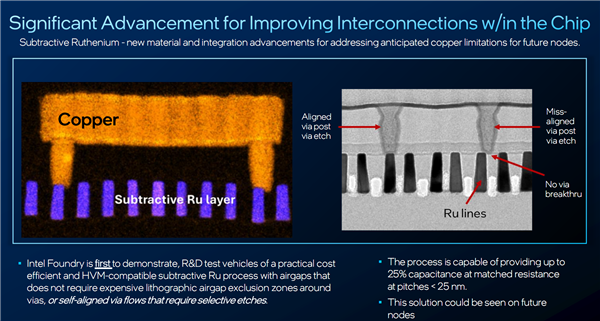

互连微缩重大进步

英特尔在微缩互连技术方面取得了显著成就。他们引入了钌作为新型金属化材料,并结合薄膜电阻率和空气间隙等因素,确保了技术的可行性和大规模生产,同时也实现了成本优势。以25纳米或更小间距为例,采用减成法钌互连技术实现的空气间隙,能将线间电容降低高达25%,显示出相较于铜镶嵌工艺的优越性,预计将在英特尔代工的后续制程中得到应用。这种技术改进在半导体制造领域有助于提高产品性能、减少能耗,对产业链整体发展具有正面影响,至于其他企业是否会跟进这一研究路径,目前尚无明确信息。

该技术优势显著,为传统互连工艺的难题带来了创新解决方案。在激烈的市场竞争中,这一工艺的进步使得Intel在行业中的地位更加稳固。

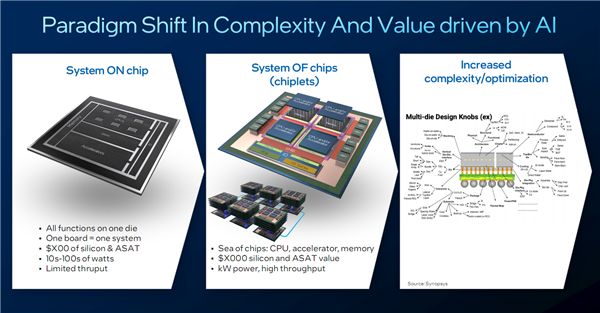

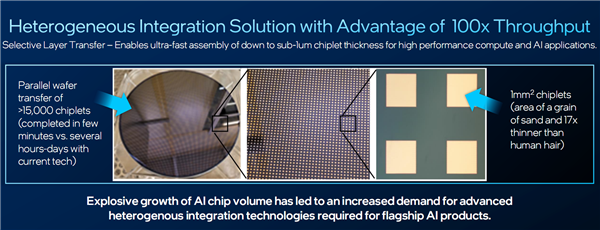

异构集成解决方案

提出了一种新型的异构集成方法。此方法能够以更灵活的方式整合超薄芯粒。与传统的芯片晶圆键合技术相比,该新方法显著减小了芯片的体积,提升了纵横比,特别是在芯片封装环节,其效率可提升至原来的100倍,实现了芯片间封装的极快速。此外,它还提高了功能密度,并与混合或融合键合工艺相结合,用于封装来自不同晶圆的芯粒。这项技术的问世,为芯片制造的布局与设计提供了新的视角,对芯片的微型化及功能强化具有重要意义。那么,这一新方法将对现有的芯片封装模式产生怎样的影响?

在当前对芯片性能提升及体积缩小的需求背景下,该方案展现出巨大的应用潜力。它有望引领芯片产业迈向一个全新的发展时期。

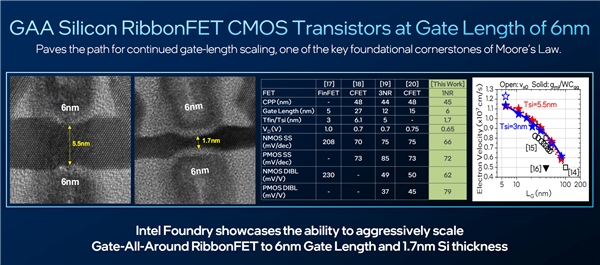

RibbonFETGAA晶体管进步

Intel展示了基于6纳米栅极长度的硅基RibbonFETCMOS晶体管。该晶体管在缩短栅极长度和沟道厚度方面表现出对短沟道效应的有效抑制和卓越性能。这些成就反映了Intel在晶体管技术领域的研发实力。在半导体制造中,晶体管性能是衡量技术水平的关键指标。此技术进展增强了Intel在高性能芯片生产中的竞争力,并为其他企业提供了提升晶体管性能的参考路径。

该成果揭示了英特尔研发战略的正确性和成效。技术逐步向市场渗透,预计将提升相关电子产品的性能,例如,手机和电脑等设备有望实现更快的运行速度和更稳定的性能。

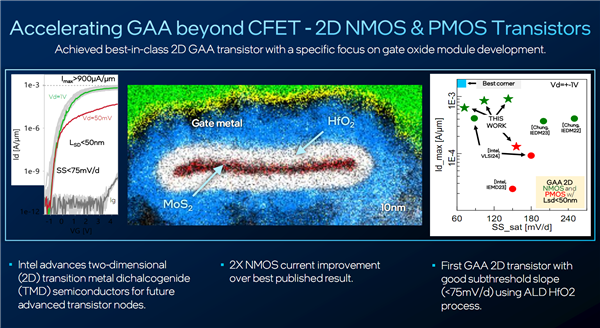

2DGAA晶体管制造研究

Intel致力于推进GAA技术的创新,其在2DGAANMOS和PMOS晶体管制造领域进行了深入研究。公司特别关注栅氧化层模块的开发,并将晶体管栅极长度缩短至30纳米。此外,2DTMD的研究也取得显著进展,预计未来可能取代硅在先进晶体管工艺中的应用。若这些研究成果得以实现商业化应用,将颠覆传统晶体管制造方式,实现晶体管的小型化和高性能化。然而,在技术大规模推广过程中,是否会出现技术兼容性问题,尚待观察。

英特尔在研究方面的不懈努力,代表了半导体技术领域的深入探索。这些前沿技术的掌握,对于确保在全球半导体市场竞争中的领先地位极为关键。

300毫米GaN方面研究

英特尔在300毫米氮化镓技术领域持续进行创新研究。他们成功制造出在300毫米GaN-on-TRSOI衬底上运行的高性能微缩增强型GaNMOSHEMT晶体管。该晶体管能有效降低信号损耗,增强信号线性度,并具备基于衬底背面处理的先进集成技术。在半导体高频、高功率应用中,此类技术突破至关重要,犹如汽车发动机的升级,将显著提升产品性能。这一技术进步将如何影响5G通信、雷达等领域的电子设备,引发行业变革?

Intel对这项技术的深入研究充分展现了其在半导体材料领域的战略布局,进一步丰富了其技术多样性,并促进了整个行业对氮化镓应用的深入研究。各位读者,Intel的这些创新成果将如何推动未来电子产品的发展?欢迎在评论区发表您的看法。如若觉得本文有所启发,敬请点赞并分享。